# ПЕРВЫЙ МИТЯП ЯЛЬЯНСЯ RISC-U

При поддержке YADRO

topic: Матричные расширения RISC-V: где, когда, куда, откуда, почему, зачем и как?;

```

.speaker {

name: Валерия Пузикова;

position: YADRO;

}

```

#### Валерия Пузикова

К.ф.-м.н., эксперт по разработке ПО, YADRO

- С 2010 года разрабатываю и реализую на C/C++ с CUDA/MPI/OpenMP численные методы для решения задач линейной алгебры, вычислительной аэрогидродинамики, AR/VR.

- Работала в Huawei, Fortum, ИСП РАН им. В.П. Иванникова, МГТУ им. Н.Э. Баумана и др.

# **YA**

## Что это? Что оно делает?

Матричные расширения ISA CPU позволяют ускорять операции над матрицами (в первую очередь умножение) без использования отдельных ускорителей.

# Что? Что делает?

Матричные расширения ISA CPU позволяют ускорять операции над матрицами (в первую очередь умножение) без использования отдельных ускорителей.

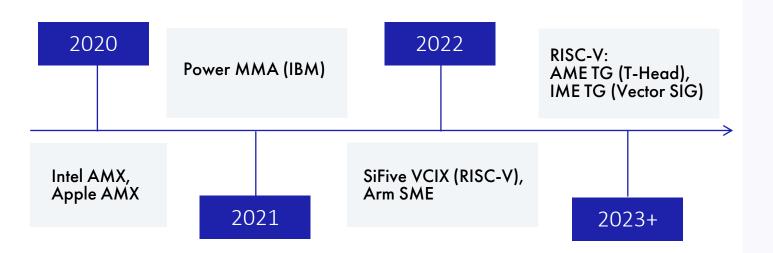

# Где? Когда?

C 2020 года: x86, Arm, Power, RISC-V.

#### Определения и обстоятельства

Разработка T-Head RVM → RISC-V AME TG

Предложения RISC-V Vector SIG —> RISC-V IME TG

Свежие вести с полей: Sparse Lives Matter

Заключение

#### Зачем?

#### Основная нагрузка – матричные операции:

- умножение плотных матриц (GEMM);

- умножение разреженной матрицы на вектор;

- прочие операции в разных пропорциях

в зависимости от конкретных приложений.

**AI/ML** – ИИ и машинное обучение.

**CV** – компьютерное зрение.

**AR/VR** – дополненная и виртуальная реальность.

**ADAS** – система помощи водителю.

**HPC** – математическое моделирование.

#### Зачем?

#### Основная нагрузка – матричные операции:

- умножение плотных матриц (GEMM);

- умножение разреженной матрицы на вектор;

- прочие операции в разных пропорциях

в зависимости от конкретных приложений.

Развитие технологий в этих областях увеличивает спрос на вычислительные мощности на порядки.

Нужно ускоряться...

# A как же GPU/TPU/...?

#### Ускорители – это прекрасно, но жизнь такова, что и на CPU тоже надо ускоряться...

- Доля матричных нагрузок велика во всех сегментах оборудования;

- Ускоритель может быть уже занят другими задачами;

- Даже в сегменте суперкомпьютеров есть гомогенные машины:

- Fujitu Fugaku (Arm A64FX)

- №2 в TOP500,

- №1 в HPCG, HPL-AI, Graph500.

## Как ускоряться без ускорителей и расширений?

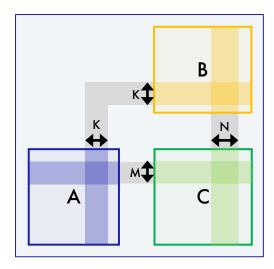

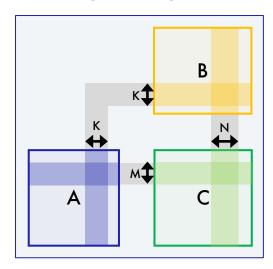

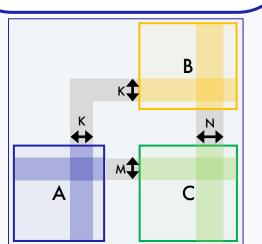

Например, рассмотрим умножение матриц

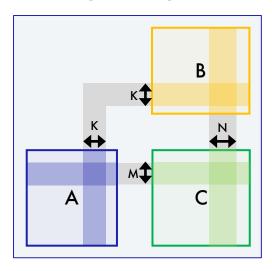

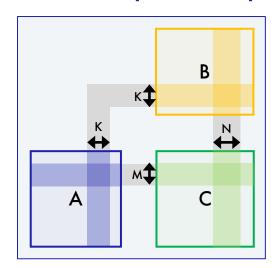

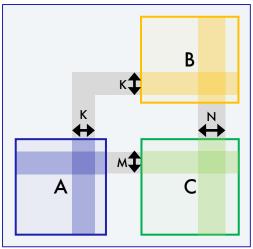

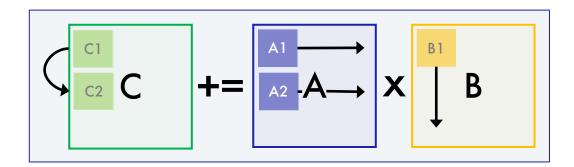

$$C_{M\times N}=A_{M\times K}\times B_{K\times N}.$$

Это  $M \cdot N$  скалярных произведений строк первого операнда на столбцы второго:

$$\begin{bmatrix} C_0^0 & \cdots & C_0^{N-1} \\ \vdots & \ddots & \vdots \\ C_{M-1}^0 & \cdots & C_{M-1}^{N-1} \end{bmatrix} = \begin{bmatrix} \sum_{k=0}^{K-1} A_0^k B_k^0 & \cdots & \sum_{k=0}^{K-1} A_0^k B_k^{N-1} \\ \vdots & \ddots & \vdots \\ \sum_{k=0}^{K-1} A_{M-1}^k B_k^0 & \cdots & \sum_{k=0}^{K-1} A_{M-1}^k B_k^{N-1} \end{bmatrix}.$$

## Как ускоряться без ускорителей и расширений?

Например, рассмотрим умножение матриц

$$C_{M\times N}=A_{M\times K}\times B_{K\times N}.$$

Алгоритм аккумуляции произведения очень прост:

$$C_{M\times N} = [0]_{M\times N},$$

for  $i = [0, M)$

for  $j = [0, N)$

for  $k = [0, K)$   $C_i^j += A_i^k B_k^j$ .

$\ni$ то  $M \cdot N \cdot K$  умножений-сложений.

Число операций не сократить...

## Как ускоряться без ускорителей и расширений?

Например, рассмотрим умножение матриц

$$C_{M\times N}=A_{M\times K}\times B_{K\times N}.$$

Алгоритм аккумуляции произведения очень прост:

$$C_{M\times N} = [0]_{M\times N},$$

for  $i = [0, M)$

for  $j = [0, N)$

for  $k = [0, K)$   $C_i^j += A_i^k B_k^j$ .

$\ni$ то  $M \cdot N \cdot K$  умножений-сложений.

Число операций не сократить...

Но скорость их выполнения может быть разной!

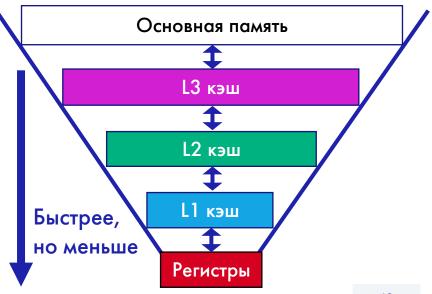

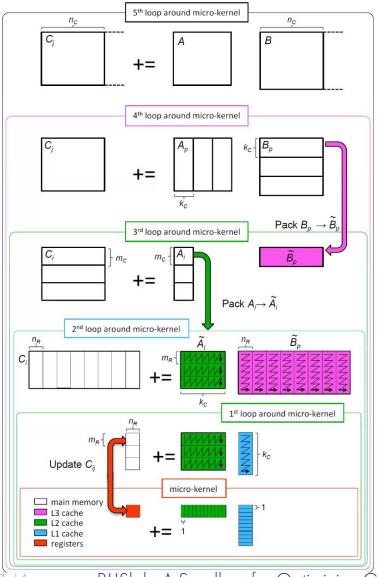

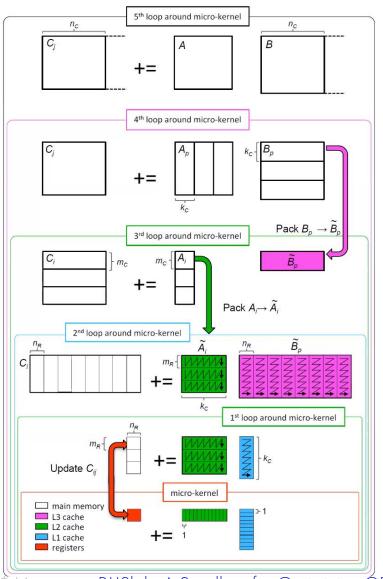

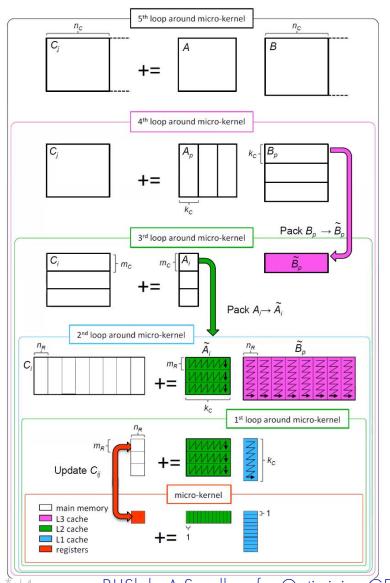

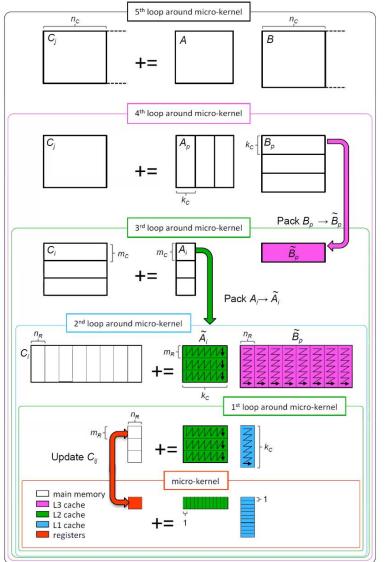

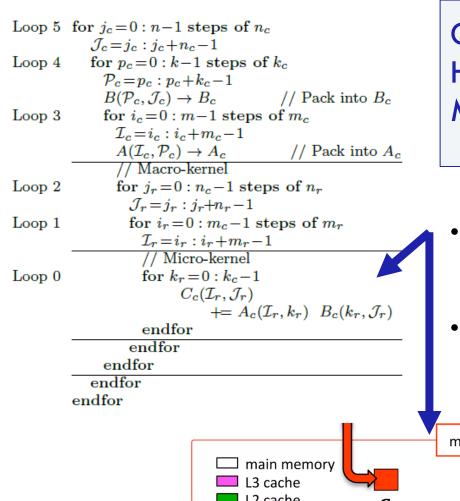

# Goto, Geijn: Anatomy of High-Performance Matrix Multiplication

• Этот подход используется в библиотеках OpenBLAS и BLIS.

# Goto, Geijn: Anatomy of High-Performance Matrix Multiplication

```

Loop 5 for j_c = 0: n-1 steps of n_c

\mathcal{J}_c = i_c : i_c + n_c - 1

for p_c = 0: k-1 steps of k_c

\mathcal{P}_c = p_c : p_c + k_c - 1

B(\mathcal{P}_c, \mathcal{J}_c) \to B_c

// Pack into B_c

for i_c = 0 : m-1 steps of m_c

Loop 3

I_c = i_c : i_c + m_c - 1

// Pack into A_c

A(\mathcal{I}_c, \mathcal{P}_c) \to A_c

// Macro-kernel

for j_r = 0: n_c - 1 steps of n_r

Loop 2

\mathcal{J}_r = j_r : j_r + n_r - 1

Loop 1

for i_r = 0 : m_c - 1 steps of m_r

\mathcal{I}_r = i_r : i_r + m_r - 1

// Micro-kernel

Loop 0

for k_r = 0 : k_c - 1

C_c(\mathcal{I}_r,\mathcal{J}_r)

+= A_c(\mathcal{I}_r, k_r) B_c(k_r, \mathcal{J}_r)

endfor

endfor

endfor

endfor

endfor

```

- Этот подход используется в библиотеках OpenBLAS и BLIS.

- В OpenBLAS оптимизация начинается с Loop 2.

# Goto, Geijn: Anatomy of High-Performance Matrix Multiplication

- Этот подход используется в библиотеках OpenBLAS и BLIS.

- В OpenBLAS оптимизация начинается с Loop 2.

- В **BLIS** оптимизация начинается с **Loop 0**, т.к. он может использоваться как часть имплементации нескольких разных алгоритмов библиотеки, что делает ее более гибкой для дальнейшего масштабирования.

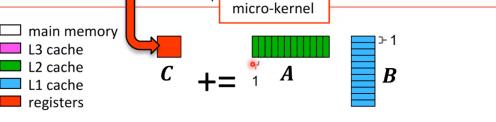

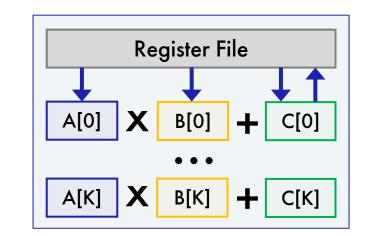

### Как ускоряться без ускорителей, но с расширениями?

Например, рассмотрим умножение матриц

$$C_{M\times N}=A_{M\times K}\times B_{K\times N}.$$

Алгоритм аккумуляции произведения очень прост:

$$C_{M\times N} = [0]_{M\times N},$$

for  $i = [0, M)$

for  $j = [0, N)$

for  $k = [0, K)$   $C_i^j += A_i^k B_k^j$ .

Это  $M \cdot N \cdot K$  умножений-сложений. И пусть M, N, K такие что, все в кэше...

Число операций не сократить...

### Как ускоряться без ускорителей, но с расширениями?

Например, рассмотрим умножение матриц

$$C_{M\times N}=A_{M\times K}\times B_{K\times N}$$

.

Алгоритм аккумуляции произведения очень прост:

$$C_{M \times N} = [0]_{M \times N},$$

for  $i = [0, M)$

for  $j = [0, N)$

for  $k = [0, K)$   $C_i^j += A_i^k B_k^j$ .

Это  $M \cdot N \cdot K$  умножений-сложений. И пусть M, N, K такие что, все в кэше...

Число операций не сократить...

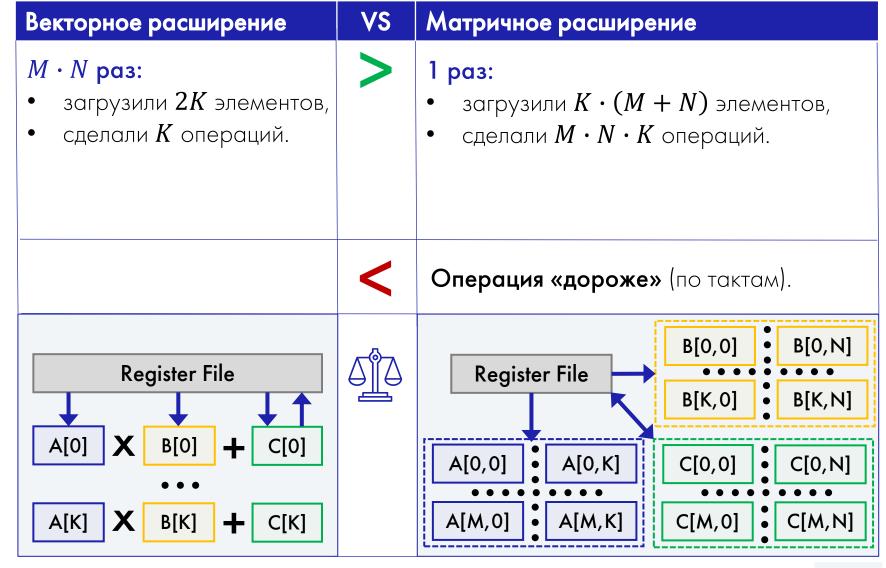

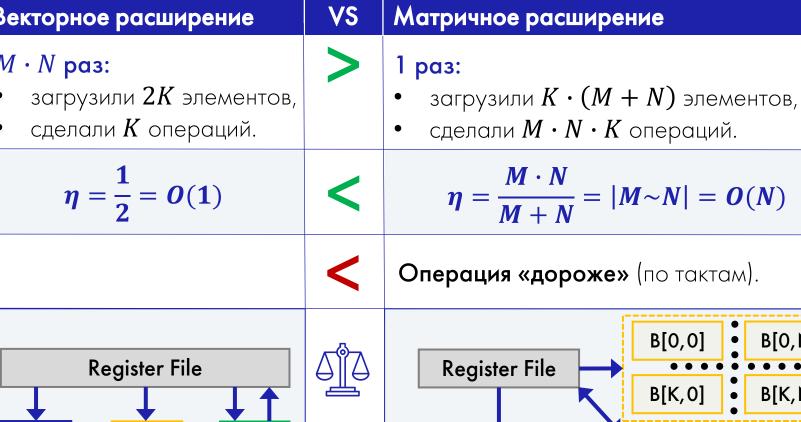

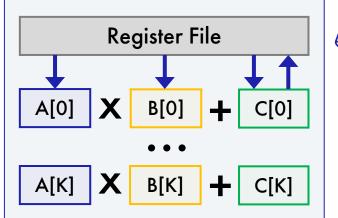

#### Но можно распараллелить!

Например, векторизовать:

- ullet загрузили 2K элементов,

- сделали K операций

и так  $M \cdot N$  раз.

### Как ускоряться без ускорителей, но с расширениями?

Например, рассмотрим умножение матриц

$$C_{M\times N}=A_{M\times K}\times B_{K\times N}$$

.

Алгоритм аккумуляции произведения очень прост:

$$C_{M\times N} = [0]_{M\times N},$$

for  $i = [0, M)$

for  $j = [0, N)$

for  $k = [0, K)$   $C_i^j += A_i^k B_k^j$ .

Это  $M \cdot N \cdot K$  умножений-сложений. И пусть M, N, K такие что, все в кэше...

Число операций не сократить.

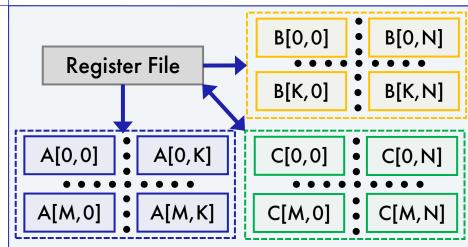

#### А можно сразу – плитками? 1 раз:

- ullet загрузили  $K \cdot (M+N)$  элементов,

- сделали  $M \cdot N \cdot K$  операций

# Ko

## Какое расширение ускоряет сильнее?

## Какое расширение ускоряет сильнее?

|   | Векторное расши                    |

|---|------------------------------------|

|   | $M \cdot N$ раз:                   |

|   | <ul> <li>загрузили 2K з</li> </ul> |

| ı | • сделали $K$ опе                  |

|   | $\eta = \frac{1}{2} = 0$           |

|   |                                    |

#### Что говорят открытые источники о производительности?

| Расширение  | Кейс                                             | Ускорение, раз | vs Vector  |

|-------------|--------------------------------------------------|----------------|------------|

| Intel AMX   | ResNet50 (batch size = 16), FP32                 | 2,2            | Intel VNNI |

| Apple AMX   | Задачи AR/VR, ML, CV                             | 2              | Neon       |

| Power MMA   | GEMM, FP64 ( $N \times 128$ , $N$ кратно 128)    | 2,6            | VSX        |

|             | LINPACK (N = $16384$ )                           | 2,2            |            |

| SiFive VCIX | GEMM, INT8                                       | 12             | RVV        |

|             | MobileNet v1 (batch size = 1),VLEN = 512 бит     | 6              |            |

| Arm SME     | GEMM, FP32 ( $M = N = K = 32256$ ), VL = 512 бит | 2,2-6,4        | SVE        |

<sup>\*</sup>Для Arm SME сравнивалось число тактов (на симуляторе). Во всех остальных случаях – время счета.

## Какие реализации лучше масштабируются?

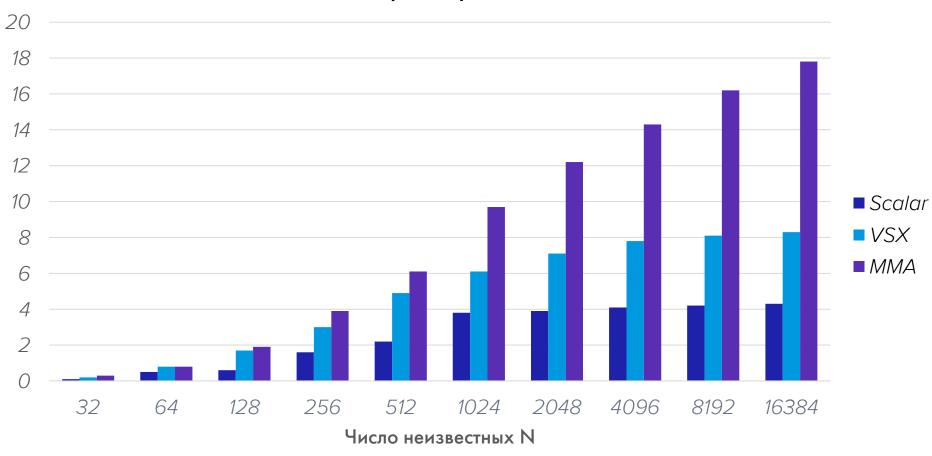

# Производительность Power 10 на LINPACK бенчмарке, flops/cycle (в зависимости от размерности задачи)

Интегрированные

SiFive Intelligence Extension

**→** Гибридные

Power MMA Arm SME

**→** Независимые

Intel AMX Apple AMX

Интегрированные

SiFive Intelligence Extension

**→** Гибридные

Power MMA Arm SME

→ Независимые

Intel AMX Apple AMX

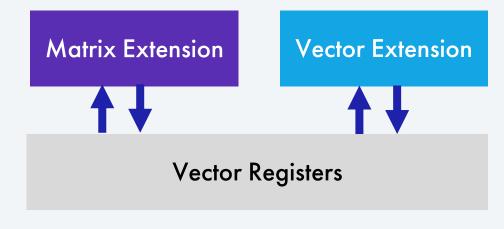

- Переиспользуют **векторные** регистры для блоков матриц-**сомножителей**.

- Переиспользуют **векторные** регистры для блоков матрицы-**аккумулятора**.

→ Интегрированные

SiFive Intelligence Extension

**► Гибридные**Power MMA

Arm SME

→ **Независимые**Intel AMX

Apple AMX

- Переиспользуют **векторные** регистры для блоков матриц-**сомножителей**.

- Вводят **независимые** регистры для блоков матрицы-**аккумулятора**.

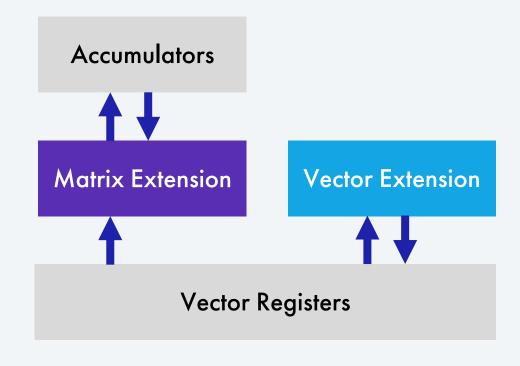

→ Интегрированные

SiFive Intelligence Extension

**► Гибридные**Power MMA

Arm SME

→ **Независимые**Intel AMX

Apple AMX

- Добавляют **матричные** регистры для блоков матриц-**сомножителей**.

- Добавляют **матричные** регистры для блоков матрицы-**аккумулятора**.

## Intel AMX (Advanced Matrix Extension)

#### Тензорные регистры – «тайлы»:

- Новый расширяемый 2D регистровый файл.

- 8 регистров ТО-Т7 (2D), по 1Кб каждый.

- Базовые операции (load/store, clear, set и т.д.)

#### TMUL – инструкции матричного умножения:

- Использует 3 регистра: Т2 += Т1 \* ТО.

- Разбивает матрицы-операнды на «тайлы».

• Пока это единственная реализованная операция над «тайлами».

## Apple AMX (Attached Matrix Extension)

Новое архитектурное пространство 5 Кб, разбито на:

- 8 х регистров, > 8 у регистров, >

каждый – 64-байтовый вектор;

- **z**, который может быть **сконфигурирован** как:

- **1** регистр  $64 \times 64 (32 \times 32)$  по 8 (32) бита;

- **2** регистра 32 x 32 по 16 бит;

- **4** регистра 16 x 16 по 32 бита;

- **8** регистров 8 x 8 по 64 бита;

- 64 регистра, каждый 64-байтовый вектор-строка.

#### Arm SME (Scalable Matrix Extension)

- Векторные (SVE/SVE2) регистры  $Z \bowtie P$  для исходных операндов.

- Вместо длины вектора VL используется SVL (Streaming Vector Length)

- SVL = {128, 256, 512, 1024, 2048} бит.

- Один новый 2D матричный регистр ZA для аккумулятора.

- $SVL_B$  строк,  $SVL_B$  размер SVL в байтах.

- $SVL_B/N$  столбцов,  $N = \{1, 4\}$  байт/элемент.

#### Поддерживается несколько операций над матрицами.

- **SME**: умножение матриц.

- **SME2:** GEMV, нелинейные решатели, разреженные матрицы.

# **T**RO

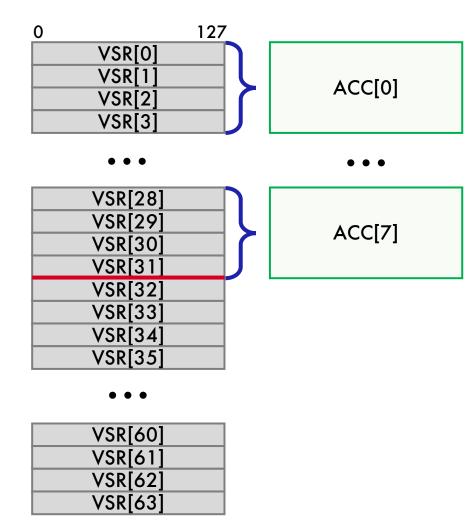

# Power MMA (Matrix-Multiply Assist)

- Это **гибридное** матричное расширение?

Позиционируется так: VSR[0..31] полностью отданы ММА.

- Восемь **512-битных аккумуляторных регистра**: каждый из 4-х регистров векторного скалярного расширения (VSX).

- Поддержка в OpenBLAS (CORE=POWER 10): оптимизации функций GEMM и TRMM для всех типов данных.

Используется в NumPy, PyTorch и других фреймворках.

- Также имеются оптимизации в **Eigen**.

Используется в OpenCV, TensorFlow и других фреймворках.

# **K**O

#### Power MMA: возможное влияние на RISC-V IME TG

- Puneeth Bhat

José Moreira

Satish Kumar Sadasivam

- Председатель RISC-V Vector SIG.

- Инициировал создание RISC-V IME TG (Integrated Matrix Extension Task Group).

- Вице-председатель RISC-V IME TG.

IBM Redbooks

Matrix-Multiply Assist Best Practices Guide

April 2021

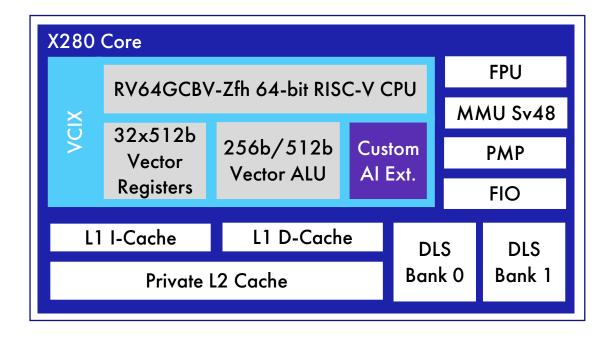

# SiFive VCIX (Vector Coprocessor Intelligence Extension)

**Кастомное** матричное расширение RISC-V, **интегрированное** в векторное.

- Появилось в 2022 г.

- 512-битные векторные регистры.

- Поддержка в TensorFlow Lite:

- оптимизированы NN операции;

- портированы многие NN модели.

# **K**O

## SiFive Intelligence Extension: доступные спецификации

- SiFive Int8 Matrix Multiplication Extensions Specification

- **Xsfvqmaccqoq** Extension: Int8 Matrix Multiplication Instructions (4-by-8 and 8-by-4) + C intrinsics.

• **Xsfvqmaccdod** Extension: Int8 Matrix Multiplication Instructions (2-by-8 and 8-by-2) + C intrinsics.

Matrix Multiply Accumulate Instruction (Bfloat 16) Xsfvfwmaccqqq

Extension Specification + C intrinsics.

# Разработка стандартных матричных расширений RISC-V

| Task Grou         | ıp (TG)                          | Integrated Matrix Extension (IME)                                                                                                                                            |                 | Attached Matrix Extension (AME)                      |                                              |  |

|-------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------|----------------------------------------------|--|

| Started on        |                                  | 11.12.2023                                                                                                                                                                   |                 | 18.10.2023                                           |                                              |  |

| Acting lea        | dership                          | Guido Araujo (Unicamp)<br>Jose Moreira (IBM)                                                                                                                                 |                 | Chou (Qiu) Jing (Alibaba)<br>Philipp Tomsich (VRULL) |                                              |  |

| Proposed workplan |                                  | Inception Requirements analysis  1 m. 4 m.                                                                                                                                   | Specification o | levelopment<br>6 m.                                  | Proof-of-concept, quantitative analysis 6 m. |  |

| Expected          | Specification                    |                                                                                                                                                                              | ISA + Intrinsi  | cs specification                                     |                                              |  |

| results           | Proof-of-concept implementations | <ul> <li>GNU binutils</li> <li>GCC with intrinsics supple</li> <li>QEMU</li> <li>LLVM MLIR</li> <li>Linux kernel (e.g., context for matrix tiles)</li> <li>oneDNN</li> </ul> |                 | <ul><li>TensorFl</li><li>PyTorch</li></ul>           | OW                                           |  |

<sup>\*</sup> Источник: <a href="https://github.com/riscv-admin/vector">https://github.com/riscv-admin/vector</a>

Определения и обстоятельства

Разработка T-Head RVM → RISC-V AME TG

Предложения RISC-V Vector SIG —> RISC-V IME TG

Свежие вести с полей: Sparse Lives Matter

Заключение

### T-Head: требования к матричному расширению RISC-V

#### • Эффективность:

повысит производительность АІ приложений за счет ускорения матричных операций.

#### • Универсальность и масштабируемость:

эффективно работает **на широком спектре оборудования** – от маломощных периферийных устройств до высокопроизводительных серверов в дата-центрах.

#### • Гибкость:

поддерживает широкий диапазон типов данных и размеров матриц.

• Переносимость двоичного кода (размеры регистров, аппаратная реализация).

#### • Перспективность:

легко расширить в будущем до полноценного Al Matrix ++ Extension.

# **EXECUTE**

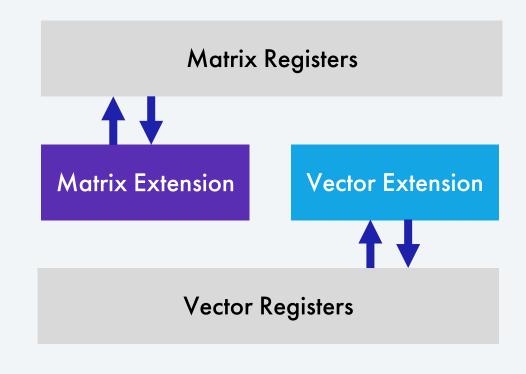

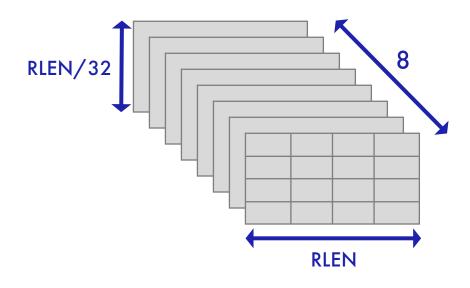

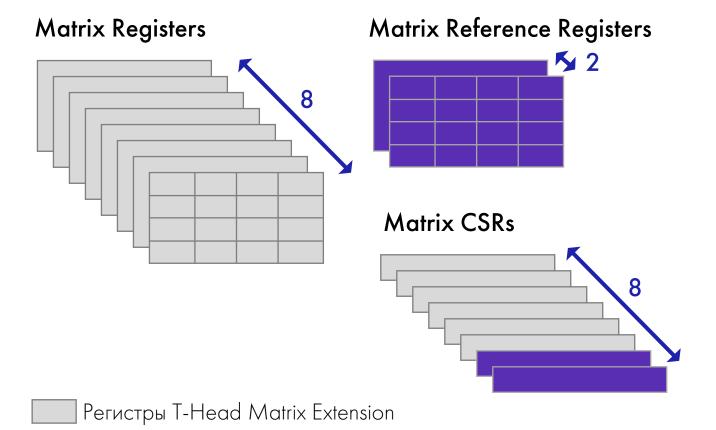

#### Матричные регистры

- Восемь 2D матричных регистров для сомножителей и аккумуляторов.

- Длина строки  $RLEN = 2^{n+6} = \{128, 256, 512, ...\}$  бит.

- Число строк RLEN  $/ 32 = 2^{n+1}$ .

- Размер регистра MLEN =  $RLEN^2 / 32 = 2^{2n+7}$  бит.

- Ширина элемента  $N = \{4, 8, 16, 32, 64\}$  бит.

- Число столбцов RLEN / N.

## T-Head RVM ISA: всего 20+ инструкций

| Группа инструкций | Количество инструкций | Краткое описание                                                                                                                                                                                    |

|-------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Matrix MACC       | 3                     | Умножение блоков матриц и аккумуляция                                                                                                                                                               |

| Matrix operations | 5                     | Прочие операции над матрицами и их частями: сложение/вычитание, векторное произведение векторов, сдвиг окна, выделение подматрицы. Число поддерживаемых операций над матрицами будет увеличиваться. |

| Memory access     | 4                     | Загрузка/выгрузка данных из матричных регистров                                                                                                                                                     |

| Move              | 6                     | Перемещение данных между регистрами (матричными или скалярными и матричными)                                                                                                                        |

| Matrix config     | 2                     | Конфигурирование матричных плиток                                                                                                                                                                   |

| Others            | 2                     | Освобождение/обнуление матричных регистров                                                                                                                                                          |

## **K**

## T-Head RVM Specification

- https://github.com/T-head-Semi/riscv-matrix-extension-spec

- Call convention for RVM: <a href="https://github.com/T-head-Semi/riscv-matrix-extension-spec/blob/master/doc/abi/riscv-cc.adoc">https://github.com/T-head-Semi/riscv-matrix-extension-spec/blob/master/doc/abi/riscv-cc.adoc</a>

- **Programmer's Model:** <a href="https://github.com/T-head-Semi/riscv-matrix-extension-spec/blob/master/spec/matrix\_body.adoc">https://github.com/T-head-Semi/riscv-matrix-extension-spec/blob/master/spec/matrix\_body.adoc</a>

- **RVM Intrinsic API:** <a href="https://github.com/T-head-Semi/riscv-matrix-extension-spec/blob/master/doc/intrinsic/rvm-intrinsic-api.adoc">https://github.com/T-head-Semi/riscv-matrix-extension-spec/blob/master/doc/intrinsic/rvm-intrinsic-api.adoc</a>

- Предлагаемая нумерация регистров: <a href="https://github.com/T-head-Semi/riscv-matrix-extension-spec/blob/master/doc/abi/riscv-dwarf.adoc">https://github.com/T-head-Semi/riscv-matrix-extension-spec/blob/master/doc/abi/riscv-dwarf.adoc</a>

- **Demo:** <a href="https://github.com/T-head-Semi/riscv-matrix-extension-spec/tree/master/demos">https://github.com/T-head-Semi/riscv-matrix-extension-spec/tree/master/demos</a>

- https://riscv.org/blog/2023/02/xuantie-matrix-multiply-extension-instructions/

#### T-Head RVM Demo

- Тулчейн (XuanTie QEMU)

- Система логирования: общая статистика, детализированная статистика по инструкциям, вызовам функций и т.д.

- **RVV и RVM реализации** для:

- GEMM (M = N = K = 160); INT8; ResNet50.

- Число инструкций сокращается в 2-14 раз по сравнению с RVV.

```

# cpf stat: gemm/gemm_fp16.elf

...../gemm_fp16.log

total cycles:

2151845

total instructions:

116361

CPI:

18.493

Read bytes:

2067351

Write bytes:

62150

[ icache ]

icache refs:

118137

instruction summary ]

instructions:

load

2671

instructions:

1339

store

abs jump instructions:

523

12219

branch

instructions:

call

instructions:

180

instructions:

0

dsp

24

vdsp

instructions:

50840

matrix

instructions:

float

instructions:

12

instructions:

rts

0

instructions:

rte

47190

alu

instructions:

```

## TA CONTROLLER

#### Call for Matrix TG

#### pre-inception stage

- Invite experts and engineers join the project

- Arrange meetings to discuss about matrix extension and Al applications

- Call for Al matrix extension spec proposals

- Gap analysis for matrix extension

#### Attached Matrix TG

Понедельник, 29 января · 6:00-6:55РМ Кажд. 2 нед. – понедельник

#### future plan

- Cooperate with other RISCV group

- OS supported(Linux/Android)

- Al framework supported(TensorFlow/PyTorch)

- Chip released including matrix extension

- Matrix++ extension

#### milestone1

- Release matrix extension spec v0.1

- Choose benchmark to value all the proposals

#### milestone2

- Release Al matrix extension spec v0.5

- Toolchain (assembler/complier etc.) ready

- Simulator/Emulator ready

#### milestone3

- Ratify Al matrix extension spec v1.0

- Matrix compatibility test suit

- Al compiler stack and library ready

<sup>2023/9 2023/12 2024/05 2024/10 2024 ~ 2026</sup>

Определения и обстоятельства

Разработка T-Head RVM → RISC-V AME TG

Предложения RISC-V Vector SIG -> RISC-V IME TG

Свежие вести с полей: Sparse Lives Matter

Заключение

#### RISC-V Vector SIG

# Chair: Jose Moreira (IBM) Vice-chair: Abel Bernabeu (Esperanto)

- Группа, ответственная за рассмотрение всех векторных расширений RISC-V ISA в будущем.

- Оценивает новые предложения, при необходимости создает свои собственные и работает над созданием целевых групп (ТG) для новых расширений.

- https://github.com/riscv-admin/vector

- Meeting minutes: <a href="https://github.com/riscv-admin/vector/tree/main/minutes">https://github.com/riscv-admin/vector/tree/main/minutes</a>

- С сентября 2023 г. рассматривали возможные варианты стандартного интегрированного матричного расширения (катализатор действия T-Head по созданию целевой группы для разработки стандартного независимого матричного расширения).

- 11 декабря 2023 г. сформировали RISC-V IME TG (Integrated Matrix Facility Task Group).

# **K**O

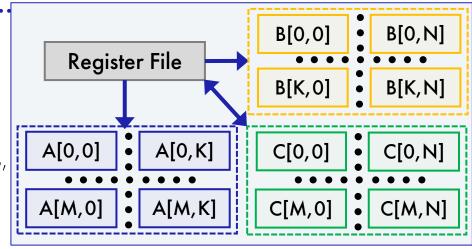

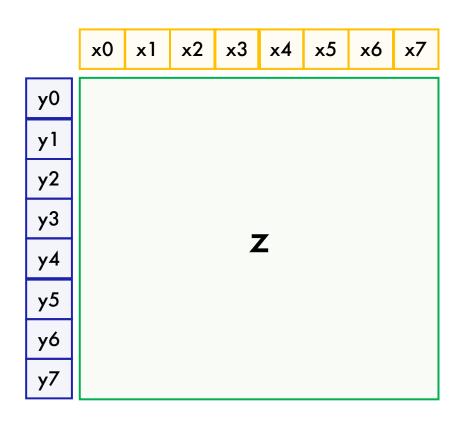

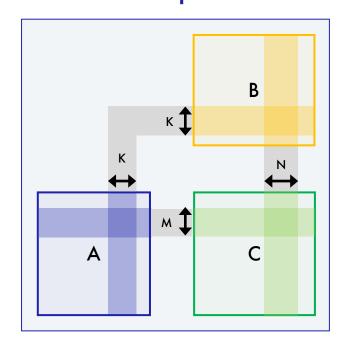

#### Общие предположения

Рассматривается умножение блоков матриц

$$C_{M\times N}=A_{M\times K}\times B_{K\times N}.$$

**Первый сомножитель** рассматриваем как **вектор** из K **столбцов**:

$$A_{M\times K}=[A^0 \quad \cdots \quad A^{K-1}].$$

Второй сомножитель рассматриваем как вектор из K строк:

$$B_{K\times N} = [B_0 \quad \cdots \quad B_{K-1}]^T$$

.

Тогда для умножения блоков можно использовать алгоритм

$$C_{M\times N} = [0]_{M\times N}$$

, for  $k = [0, K)$   $C_{M\times N} += A^k \times B_k$ .

Таким образом, рассматриваем внешнее произведение векторов:

$$A^{k} \times B_{k} = \begin{bmatrix} A_{0}^{k} \\ \vdots \\ A_{M-1}^{k} \end{bmatrix} \times \begin{bmatrix} B_{k}^{0} & \cdots & B_{k}^{N-1} \end{bmatrix} = \begin{bmatrix} A_{0}^{k} B_{k}^{0} & \cdots & A_{0}^{k} B_{k}^{N-1} \\ \vdots & \ddots & \vdots \\ A_{M-1}^{k} B_{k}^{0} & \cdots & A_{M-1}^{k} B_{k}^{N-1} \end{bmatrix}.$$

## TA CONTROLLER

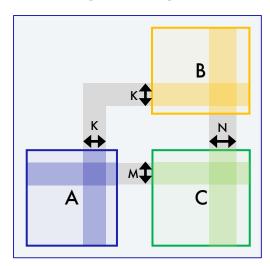

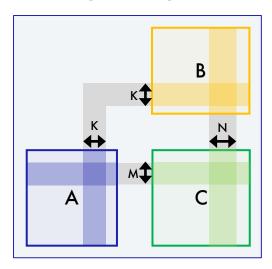

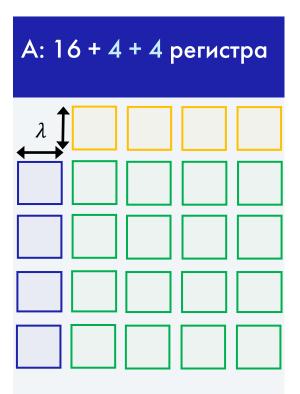

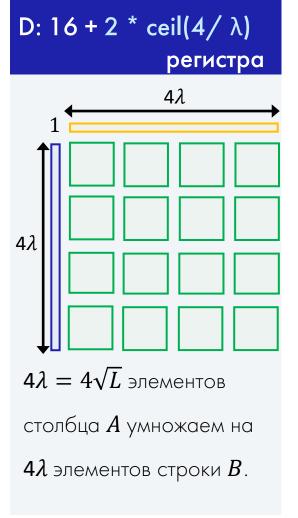

#### Определение размеров блоков

Goto, Geijn: Anatomy of High-Performance Matrix Multiplication

- Рассматривается уровень micro-kernel, как в библиотеке **BLIS**.

- Может быть частью имплементации разных алгоритмов.

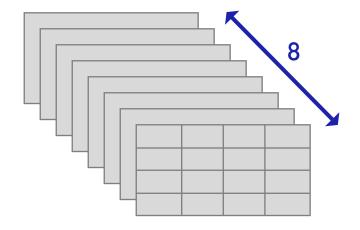

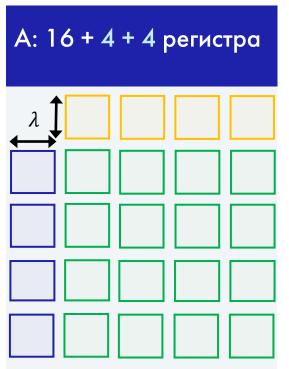

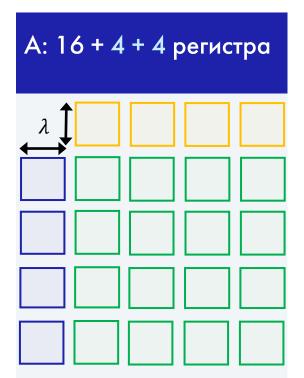

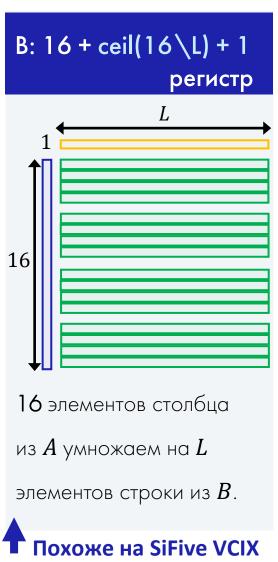

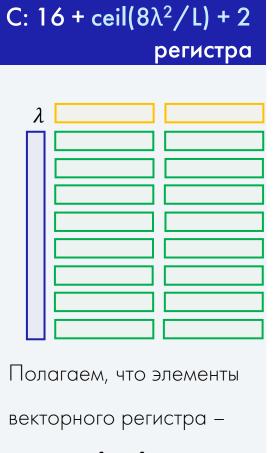

#### Общие предположения о регистрах

- Архитектурное пространство состоит из 32 векторных регистров.

- ullet Число элементов, помещающихся в один регистр, обозначим как L .

- Векторные регистры используются как для блоков двух матриц-сомножителей, так и для блоков матрицы-аккумулятора.

- Под блоки матрицы-аккумулятора отводится 16 векторных регистров. 🔷 Половина, как в Power MMA

- Число регистров, используемых для хранения элементов блоков матриц-сомножителей, обсуждается.

- Определит, сколько элементов матриц А и В будет загружаться.

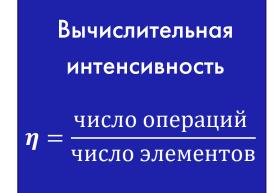

- Вычислительная интенсивность  $\eta = \frac{$ число операций mul-add операций / элемент.

• Все плитки матриц

$$\lambda \times \lambda$$

,  $\lambda = \sqrt{L}$ .

• 1 плитка на регистр.

• Все плитки матриц

$$\lambda \times \lambda$$

,  $\lambda = \sqrt{L}$ .

• 1 плитка на регистр.

- Все плитки матриц

- $\lambda \times \lambda$ ,  $\lambda = \sqrt{L}$ .

- 1 плитка на регистр.

- Все плитки матриц

- $\lambda \times \lambda$ ,  $\lambda = \sqrt{L}$ .

- 1 плитка на регистр.

Полагаем, что элементы векторного регистра матрицы  $\lambda \times \lambda$ .

## IME Task Group Proposal

- HPC's GEMM as the use case for the extension.

- Goal: ~90% peak performance for GEMM kernels; ~2x performance (vs vector) for other kernels.

- Data types for HPC use cases (32, 64-bit).

- The added data types for AI/ML: (4, 8, 16-bit).

- For a blue-print of the software kernel that we are accelerating we should look at the <u>BLIS microkernel</u>.

- The deliveries will be assumed :

- specification of the operations,

- instruction encoding,

- compiler & simulation support,

- library code development.

Определения и обстоятельства

Разработка T-Head RVM → RISC-V AME TG

Предложения RISC-V Vector SIG —> RISC-V IME TG

Свежие вести с полей: Sparse Lives Matter

Заключение

#### Vector SIG: первые обсуждения Sparse Matrix Extension

Нам следует включить разреженность в матричные расширения версии 2.0.

Нужно убедиться, что версия 1.0 не исключает этого.

Разреженность — это сложная проблема, и именно поэтому ее нужно начинать обсуждать как можно раньше.

Что еще более важно, сейчас самое время начать это обсуждение, если мы хотим перехватить работу над SparseBLAS.

Хосе Морейра, председатель RISC-V Vector SIG

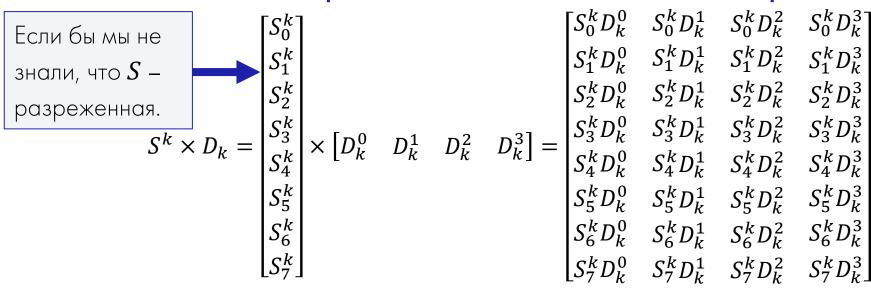

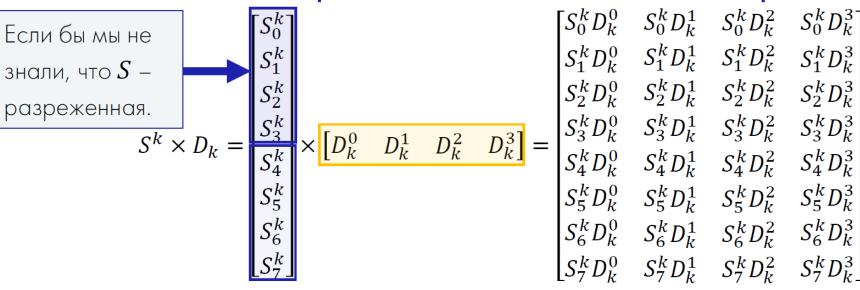

#### Общие предположения

# Some thoughts on sparsity support for RISC-V matrix extensions

José Moreira IBM Research Рассматривается умножение блоков разреженной и плотной матриц

$$R_{M\times N}=S_{M\times K}\times D_{K\times N}.$$

Первый сомножитель – вектор из K разреженных столбцов:

$$S_{M\times K}=[S^0 \quad \cdots \quad S^{K-1}].$$

Разреженность (sparsity – % нулевых элементов) ≈ 50-90%

(характерно для матриц весов из DL моделей, для HPC – выше).

Второй сомножитель – вектор из K плотных строк:

$$D_{K\times N}=[D_0 \quad \cdots \quad D_{K-1}]^T$$

.

Тогда для умножения блоков можно использовать алгоритм

$$R_{M\times N} = [0]_{M\times N}$$

, for  $k = [0, K)$   $R_{M\times N} += S^k \times D_k$ .

Аккумулятор – плотная матрица.

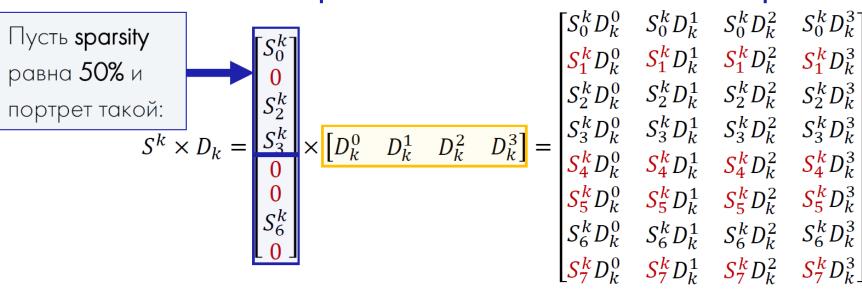

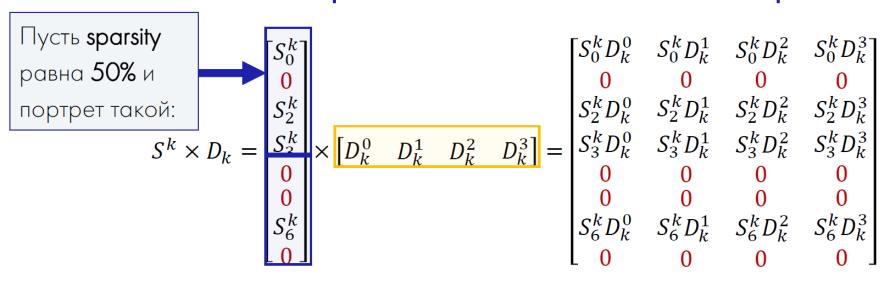

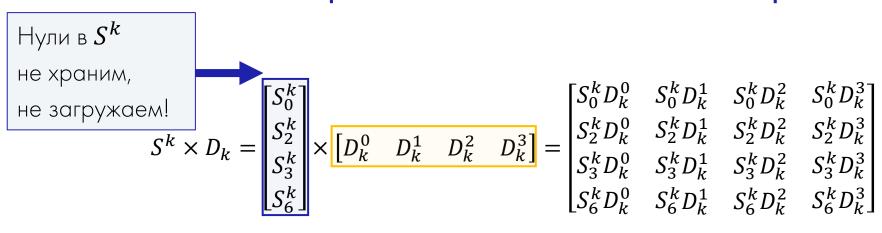

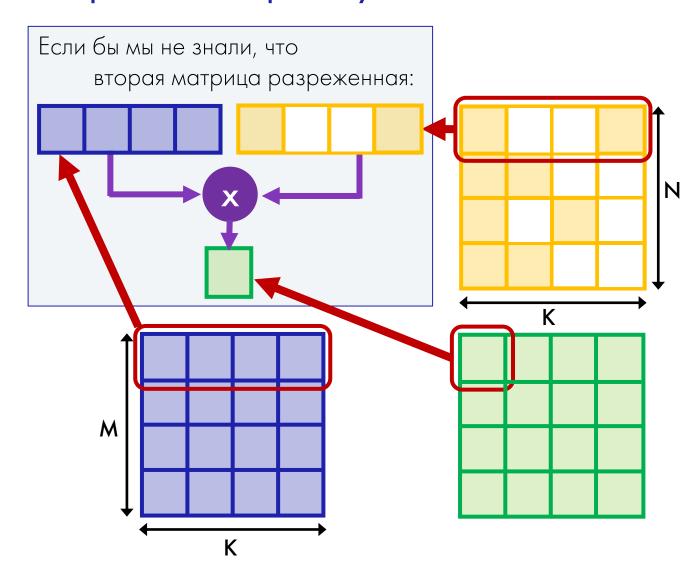

#### В чем отличие от произведения плотных матриц?

Для примера рассмотрим случай M=8, N=4.

# **K**O

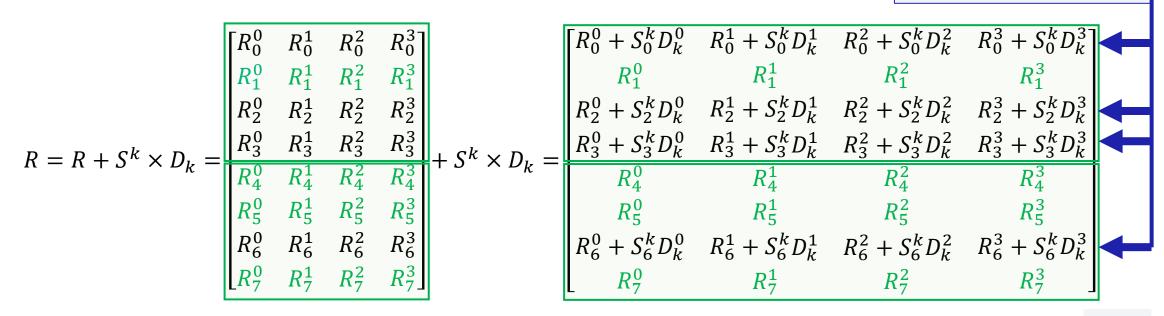

#### В чем отличие от произведения плотных матриц?

$$R = R + S^{k} \times D_{k} = \begin{bmatrix} R_{0}^{0} & R_{0}^{1} & R_{0}^{2} & R_{0}^{3} \\ R_{1}^{0} & R_{1}^{1} & R_{1}^{2} & R_{1}^{3} \\ R_{2}^{0} & R_{1}^{1} & R_{1}^{2} & R_{2}^{3} \\ R_{3}^{0} & R_{3}^{1} & R_{3}^{2} & R_{3}^{3} \\ R_{5}^{0} & R_{5}^{1} & R_{5}^{2} & R_{5}^{3} \\ R_{6}^{0} & R_{6}^{1} & R_{6}^{2} & R_{6}^{3} \\ R_{7}^{0} & R_{7}^{1} & R_{7}^{2} & R_{7}^{3} \end{bmatrix} + S^{k} \times D_{k} = \begin{bmatrix} R_{0}^{0} + S_{0}^{k}D_{k}^{0} & R_{0}^{1} + S_{0}^{k}D_{k}^{1} & R_{0}^{2} + S_{0}^{k}D_{k}^{2} & R_{0}^{3} + S_{0}^{k}D_{k}^{3} \\ R_{0}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{1} & R_{1}^{2} + S_{1}^{k}D_{k}^{2} & R_{1}^{3} + S_{1}^{k}D_{k}^{3} \\ R_{0}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{1} & R_{1}^{2} + S_{1}^{k}D_{k}^{2} & R_{1}^{3} + S_{1}^{k}D_{k}^{3} \\ R_{0}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{1} & R_{1}^{2} + S_{1}^{k}D_{k}^{2} & R_{1}^{3} + S_{1}^{k}D_{k}^{3} \\ R_{0}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{1} & R_{1}^{2} + S_{1}^{k}D_{k}^{2} & R_{2}^{3} + S_{2}^{k}D_{k}^{3} \\ R_{0}^{0} + S_{0}^{1}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{0} & R_{1}^{2} + S_{2}^{k}D_{k}^{2} & R_{1}^{3} + S_{1}^{k}D_{k}^{3} \\ R_{1}^{0} + S_{1}^{0}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{1} & R_{1}^{2} + S_{1}^{k}D_{k}^{2} & R_{2}^{3} + S_{2}^{k}D_{k}^{3} \\ R_{1}^{0} + S_{1}^{0}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{0} & R_{1}^{2} + S_{2}^{k}D_{k}^{0} & R_{1}^{2} + S_{2}^{k}D_{k}^{0} \\ R_{2}^{0} + S_{2}^{0}D_{k}^{0} & R_{1}^{1} + S_{1}^{1}D_{k}^{1} & R_{2}^{2} + S_{2}^{k}D_{k}^{0} & R_{3}^{3} + S_{3}^{k}D_{k}^{0} \\ R_{2}^{0} + S_{2}^{0}D_{k}^{0} & R_{1}^{1} + S_{2}^{0}D_{k}^{1} & R_{2}^{2} + S_{2}^{0}D_{k}^{0} & R_{3}^{2} + S_{3}^{0}D_{k}^{0} \\ R_{2}^{0} + S_{2}^{0}D_{k}^{0} & R_{1}^{1} + S_{2}^{0}D_{k}^{0} & R_{1}^{1} + S_{2}^{0}D_{k}^{0} & R_{2}^{1} + S_{3}^{0}D_{k}^{0} \\ R_{2}^{0} + S_{2}^{0}D_{k}^{0} & R_{1}^{1} + S_{2}^{0}D_{k}^{0} & R_{1}^{1} + S_{2}^{0}D_{k}^{0} & R_{2}^{1} + S_{2}^{0}D_{k}^{0} \\ R_{2}^{0} + S_{2}^{0}D_{k}^{0}$$

# Ko

#### В чем отличие от произведения плотных матриц?

$$R = R + S^{k} \times D_{k} = \begin{bmatrix} R_{0}^{0} & R_{0}^{1} & R_{0}^{2} & R_{0}^{3} \\ R_{1}^{0} & R_{1}^{1} & R_{1}^{2} & R_{1}^{3} \\ R_{2}^{0} & R_{1}^{1} & R_{2}^{2} & R_{2}^{3} \\ R_{3}^{0} & R_{3}^{1} & R_{3}^{2} & R_{3}^{3} \\ R_{3}^{0} & R_{3}^{1} & R_{3}^{2} & R_{3}^{3} \\ R_{4}^{0} & R_{1}^{1} & R_{4}^{2} & R_{4}^{3} \\ R_{5}^{0} & R_{5}^{1} & R_{5}^{2} & R_{5}^{3} \\ R_{6}^{0} & R_{6}^{1} & R_{6}^{2} & R_{6}^{3} \\ R_{7}^{0} & R_{7}^{1} & R_{7}^{2} & R_{7}^{3} \end{bmatrix} + S^{k} \times D_{k} = \begin{bmatrix} R_{0}^{0} + S_{0}^{k}D_{k}^{0} & R_{1}^{1} + S_{0}^{k}D_{k}^{1} & R_{0}^{2} + S_{0}^{k}D_{k}^{2} & R_{0}^{3} + S_{0}^{k}D_{k}^{3} \\ R_{1}^{0} + S_{1}^{k}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{0} & R_{1}^{2} + S_{2}^{k}D_{k}^{2} & R_{1}^{3} + S_{1}^{k}D_{k}^{3} \\ R_{1}^{0} + S_{1}^{k}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{0} & R_{1}^{2} + S_{2}^{k}D_{k}^{2} & R_{1}^{3} + S_{1}^{k}D_{k}^{3} \\ R_{2}^{0} + S_{2}^{k}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{0} & R_{1}^{2} + S_{2}^{k}D_{k}^{2} & R_{2}^{3} + S_{2}^{k}D_{k}^{3} \\ R_{2}^{0} + S_{2}^{k}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{0} & R_{1}^{2} + S_{2}^{k}D_{k}^{2} & R_{2}^{3} + S_{2}^{k}D_{k}^{3} \\ R_{2}^{0} + S_{2}^{k}D_{k}^{0} & R_{3}^{1} + S_{3}^{k}D_{k}^{1} & R_{2}^{2} + S_{2}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{3}^{0} + S_{3}^{k}D_{k}^{0} & R_{3}^{1} + S_{3}^{k}D_{k}^{1} & R_{3}^{2} + S_{3}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{3}^{0} + S_{3}^{k}D_{k}^{0} & R_{1}^{1} + S_{3}^{k}D_{k}^{1} & R_{2}^{2} + S_{2}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{3}^{0} + S_{3}^{k}D_{k}^{0} & R_{1}^{1} + S_{3}^{k}D_{k}^{1} & R_{2}^{2} + S_{2}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{3}^{0} + S_{3}^{0}D_{k}^{0} & R_{1}^{1} + S_{3}^{1}D_{k}^{1} & R_{2}^{2} + S_{2}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{3}^{0} + S_{3}^{0}D_{k}^{0} & R_{1}^{1} + S_{3}^{1}D_{k}^{1} & R_{2}^{2} + S_{3}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{3}^{0} + S_{3}^{0}D_{k}^{0} & R_{1}^{1} + S_{3}^{1}D_{k}^{0} & R_{1}^{1} + S_{3}^{1}D_{k}^{1} & R_{2}^{2} + S_{$$

# Ko

#### В чем отличие от произведения плотных матриц?

$$R = R + S^{k} \times D_{k} = \begin{bmatrix} R_{0}^{0} & R_{0}^{1} & R_{0}^{2} & R_{0}^{3} \\ R_{1}^{0} & R_{1}^{1} & R_{1}^{2} & R_{1}^{3} \\ R_{2}^{0} & R_{1}^{1} & R_{1}^{2} & R_{1}^{3} \\ R_{3}^{0} & R_{3}^{1} & R_{3}^{2} & R_{3}^{3} \\ R_{3}^{0} & R_{3}^{1} & R_{3}^{2} & R_{3}^{3} \\ R_{4}^{0} & R_{1}^{1} & R_{4}^{2} & R_{4}^{3} \\ R_{5}^{0} & R_{5}^{1} & R_{5}^{2} & R_{5}^{3} \\ R_{6}^{0} & R_{6}^{1} & R_{6}^{2} & R_{6}^{3} \\ R_{7}^{0} & R_{7}^{1} & R_{7}^{2} & R_{7}^{3} \end{bmatrix} + S^{k} \times D_{k} = \begin{bmatrix} R_{0}^{0} + S_{0}^{k}D_{k}^{0} & R_{0}^{1} + S_{0}^{k}D_{k}^{1} & R_{0}^{2} + S_{0}^{k}D_{k}^{2} & R_{0}^{3} + S_{0}^{k}D_{k}^{3} \\ R_{1}^{0} + S_{1}^{k}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{1} & R_{1}^{2} + S_{1}^{k}D_{k}^{2} & R_{1}^{3} + S_{1}^{k}D_{k}^{3} \\ R_{1}^{0} + S_{1}^{k}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{0} & R_{1}^{1} + S_{1}^{k}D_{k}^{2} & R_{1}^{3} + S_{1}^{k}D_{k}^{3} \\ R_{2}^{0} + S_{2}^{k}D_{k}^{0} & R_{1}^{1} + S_{2}^{k}D_{k}^{1} & R_{2}^{2} + S_{2}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{2}^{0} + S_{2}^{k}D_{k}^{0} & R_{1}^{1} + S_{2}^{k}D_{k}^{1} & R_{2}^{2} + S_{2}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{2}^{0} + S_{2}^{k}D_{k}^{0} & R_{1}^{1} + S_{2}^{k}D_{k}^{1} & R_{2}^{2} + S_{2}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{3}^{0} + S_{3}^{k}D_{k}^{0} & R_{1}^{1} + S_{2}^{k}D_{k}^{1} & R_{2}^{2} + S_{2}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{3}^{0} + S_{3}^{k}D_{k}^{0} & R_{1}^{1} + S_{3}^{k}D_{k}^{1} & R_{2}^{2} + S_{2}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{3}^{0} + S_{5}^{k}D_{k}^{0} & R_{1}^{1} + S_{3}^{k}D_{k}^{1} & R_{2}^{2} + S_{2}^{k}D_{k}^{2} & R_{3}^{3} + S_{3}^{k}D_{k}^{3} \\ R_{3}^{0} + S_{3}^{0}D_{k}^{0} & R_{1}^{1} + S_{3}^{0}D_{k}^{1} & R_{2}^{2} + S_{3}^{0}D_{k}^{2} & R_{3}^{3} + S_{3}^{0}D_{k}^{3} \\ R_{3}^{0} + S_{3}^{0}D_{k}^{0} & R_{1}^{1} + S_{3}^{0}D_{k}^{1} & R_{2}^{2} + S_{3}^{0}D_{k}^{2} & R_{3}^{3} + S_{3}^{0}D_{k}^{3} \\ R_{3}^{0} + S_{3}^{0}D_{k}^{0} & R_{1}^{1} + S_{3}^{0}D_{k}^{0} & R_{1}^{1} + S_{3}^{0}D_{k}^{1} & R_{2}^{2} + S_{$$

# Ko

#### В чем отличие от произведения плотных матриц?

- На блок  $S^k$  нужно меньше регистров.

- Нужно загружать маску портрета, чтобы обновлять верные строки

аккумуляторов.

#### Разработка Sparsity Subset в XuanTie Matrix Extension

#### Отличия от предыдущего подхода:

1. Плотная матрица и разреженная поменялись местами:

$$R_{M\times N}=D_{M\times K}\times S_{K\times N}.$$

- 2. Разреженную матрицу предварительно транспонируем.

- 3. Вместо внешнего произведения векторов используем скалярное:

$$R_{M\times N} = [0]_{M\times N},$$

for  $k = [0, K)$   $R_{M\times N} += D_k \cdot S^k$ .

# **K**O

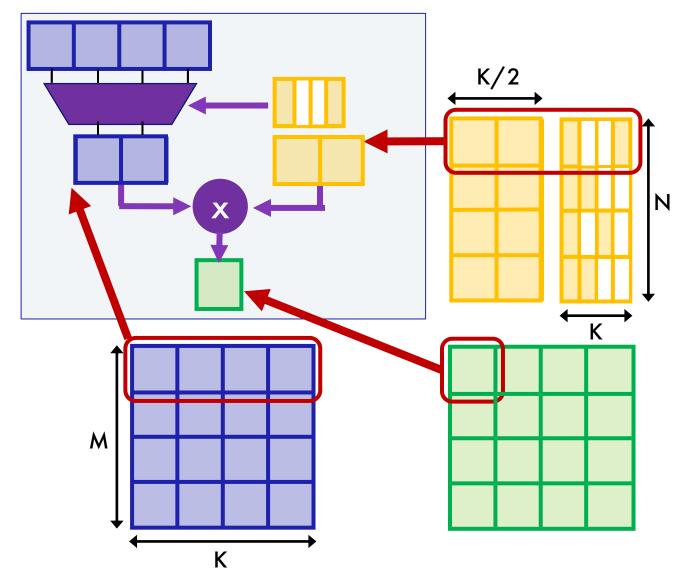

#### Разработка Sparsity Subset в XuanTie Matrix Extension

#### Отличия от предыдущего подхода:

- Маска индексов портрета

загружается в отдельный регистр.

- 2. Через маску портрета «просеиваем» не аккумуляторы, а строки плотной матрицы.

- 3. «Просеянную» плотную матрицу умножаем на разреженную (уже хранящуюся в формате без нулей) как обычные плотные матрицы.

#### Дополнительные регистры и инструкции

Регистры, добавленные для Sparsity Subset

- + **2 матричных 2D регистра** для маски индексов портрета.

- + 2 control state регистра (CSR):

- Число элементов

в одном разреженном блоке.

- Разреженность (доля нулевых элементов).

- + 3 инструкции Sparse Matrix MACC.

- + **6** инструкций **Memory access** для регистров маски индексов портрета.

Определения и обстоятельства

Разработка T-Head RVM → RISC-V AME TG

Предложения RISC-V Vector SIG —> RISC-V IME TG

Свежие вести с полей: Sparse Lives Matter

Заключение

#### Заключение

- Матричные расширения стали появляться не так давно с 2020 года. В этом плане x86, Power, Arm и RISC-V почти наравне.

- Подходят для ускорения AI/ML, AR/VR, CV, ADAS, HPC.

- Хороший ход поддержка в **OpenBLAS** и **Eigen** (как у Power MMA).

- Стандартные матричные расширения RISC-V: **Стандартные матричные расширения**

- RISC-V Attached Matrix Extension (T-Head via AME TG):

- specification <a href="https://github.com/T-head-Semi/riscv-matrix-extension-speciments">https://github.com/T-head-Semi/riscv-matrix-extension-speciments</a>

- 20+ matrix instructions, 8 matrix registers

- AI/ML Data Types

- ~9.5x performance (demos)

- RISC-V Integrated Matrix Extension (Vector SIG via IME TG):

- HPC GEMM (BLIS microkernel)

- HPC & AI/ML Data Types

- Goal: ~90% peak performance (GEMM); ~2x performance (vs vector).

- Поддержке разреженных матриц быть!

- (!) Обновления на <u>Github</u>:

- **Vector SIG**

- **IME TG**

- **AME TG**

Москва, ул. Рочдельская, 15, стр. 13 +7 800 777-06-11

yadro.com