# FPGA-Systems 2024.1

Применение плат FPGA в задачах промышленной автоматизации

Хлуденьков Александр

# Применение плат FPGA в задачах промышленной автоматизации

# производством?

### Сравнение рабочих параметров

Сравним! VS

- 1) Порты ввода-вывода (DI, DO, AI, AO).

- 2) Интерфейсы и протоколы.

- 3) Мощность процессора (MHz и разрядность).

- 4) Среда разработки.

- 1) Имеются, настраиваются.

- 2) Реализуются.

- 3) MHz и LUT.

- 4) HDL.

# Интерфейсы и протоколы

|                               | Тип              | Рабочее<br>напряжение | Скорость   | Размер<br>программы | Плата                    |

|-------------------------------|------------------|-----------------------|------------|---------------------|--------------------------|

| I2C                           | Master-<br>Slave | 3,3 B                 | 100 кб/сек | 1 кБ                | Cyclone III EP3C10E144C8 |

| SPI                           | Master-<br>Slave | 3,3 B                 | 50 Мб/сек  | 2 кБ                | Max II EPM240T100C5N     |

| UART                          |                  | 3,3 B                 | 921 кб/сек | 2 кБ                | Max II EPM240T100C5N     |

| Modbus<br>(поверх RS-<br>485) | Master-<br>Slave | -7 В до +12 В         | 115 кб/сек | 5 кБ                | Cyclone IV EP4CE6        |

| EtherCat                      | Master-<br>Slave |                       | 100 Мбит/с |                     | Stratix 10               |

# Среда разработки и исполнения

VS

| МЭК 61131-3 | Тип среды разработки | HDL       |

|-------------|----------------------|-----------|

| IL          | Текстовый            | Языки HDL |

| CFC         | Графический          | Схемы FB  |

| FBD         | Графический          | Схемы FB  |

| ST          | Текстовый            | Языки HDL |

| SFC         | Графический          | HLS       |

### Классы ПЛК

| Класс                                    | Уровень   | ПЛК             | FPGA       |

|------------------------------------------|-----------|-----------------|------------|

| PLC (Programmable Logic Controller)      | Начальный | ОВЕН ПР-200     | DE-10 Lite |

| PAC (Programmable Automation Controller) | Средний   | Siemens S7-1500 | DE2-115    |

| IPC (Industrial PC)                      | Высокий   | Cypcut-8000     | Stratix-10 |

# DE-10 Lite vs OBEH ΠΡ-200

#### DE-10Lite.

• Кристалл: MAX10 10M50DAF484C7G

• Тактовая частота: 50 МГц

• Количество элементов: 50 000

• PIN: 2x20

• IDE: Quartus

#### ПР-200.

Процессор: STM-32

• Тактовая частота: 72 МГц

• ОЗУ: 32 кБ

• Дискретные входы: 8

• Интерфейс RS-485 (до 2 шт.)

• IDE: визуальная Owen Logic

# DE2-115 vs Siemens S7-1500

#### DE2-115.

- Кристалл: Cyclone IV EP4CE115

- Тактовая частота: до 200 МГц

- Количество элементов: 114 480

- IDE: Quartus.

#### Siemens S7-1500.

- Процессор: 6ES7518-4AP00-0AB0

- Тактовая частота: 1,5 ГГц

- ОЗУ: 2 МБ

- IDE: визуальная Simatic Step 7.

# Stratix-10 vs Cypcut-8000

#### Stratix-10.

• Кристалл: Stratix-10

• Тактовая частота: 1 ГГц

• Количество элементов: 2,8 млн

• IDE: Altera SDK.

#### Cypcut-8000.

• Процессор: Intel i5

• Тактовая частота: 4 ГГц

• ОЗУ: 8 ГБ

• IDE: встроенная Cypcut

# Типовые задачи автоматизации

| Уровень задачи | Пример задачи                         | FPGA       |

|----------------|---------------------------------------|------------|

| Начальный      | Управление лифтом                     | DE-10Lite  |

| Средний        | Управление фрезерным<br>станком с ЧПУ | DE2-115    |

| Высокий        | Робототехническая линия               | Stratix-10 |

### Процесс управления лифтом

| Количество<br>этажей | Общая концепция      |

|----------------------|----------------------|

| До 5                 | Комбинационная схема |

| 6-10                 | Конечный автомат     |

| Свыше 10             | Софт-процессор       |

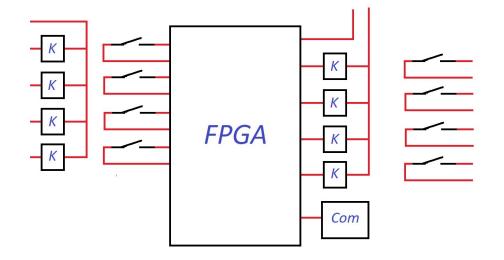

### Разработка контроллера на FPGA

#### Необходимо реализовать:

- аппаратная часть: защищенные порты ввода-вывода, увеличить количество портов.

- программная часть: среда разработки, библиотека макроблоков.

### Заключение

| Преимущество FPGA                      |                                                               |

|----------------------------------------|---------------------------------------------------------------|

| Где применять                          | Высокоскоростные устройства с большим количеством интерфейсов |

| Что для этого нужно: аппаратная часть  | Усилить порты ввода вывода                                    |

| Что для этого нужно: программная часть | Реализовать макроязык проектирования                          |

Генеральный партнёр конференции FPGA-Systems 2024.1

Первая современная отечественная САПР, реализующая сквозной цикл проектирования печатных плат

# Где найти FPGA / RTL / Verification комьюнити?

# FPGA-Systems.ru

Сайт комьюнити

# **FPGA-Systems Magazine (FSM)**

Первый журнал о программируемой логике

# @fpgasystems

Телеграм чат

# admin@fpga-systems.ru

Электронная почта

# Youtube.com/c/fpgasystems

Youtube канал