ПЛИС для начинающих: что нужно знать FPGA-инженеру

с помощью нейросети

Аббревиатура ПЛИС (FPGA) звучит как что-то сложное и нишевое — где-то между микроэлектроникой и магией. Но за ней скрывается логичная и удивительно красивая идея: возможность собрать нужное цифровое устройство прямо внутри микросхемы, описав его структуру. Именно поэтому ПЛИС используют в самых разных инженерных направлениях: прототипировании, телеком-проектах, промышленной электронике, вычислительной технике.

Виктория Ващенко, ведущий разработчик из AO «Телум», рассказывает, что такое ПЛИС и как они устроены, чем проектирование для них отличается от классического программирования, какие этапы проходит проект от идеи до воплощения в железе и почему в ПЛИС важны не только алгоритмы, но и временные параметры сигналов.

- что такое ПЛИС

- чем разработка на ПЛИС отличается от классического программирования

- как выбрать между ПЛИС, микроконтроллером и ASIC

- какие навыки необходимы FPGA-инженеру

Концепция ПЛИС: гибкая аппаратная платформа

ПЛИС — это программируемая логическая интегральная схема, то есть микросхема без заранее заданного назначения. По сути, это аппаратная заготовка. После загрузки конфигурационный файл определяет, как будут соединены тысячи логических ячеек внутри кристалла. Мы мысленно можем представить это как создание схемы из стандартных программируемых блоков и проводников.

На основе одной и той же ПЛИС инженер может разрабатывать новое цифровое устройство, меняя его конфигурацию. Это возможно благодаря двум особенностям устройства:

- Архитектура сочетает фиксированные блоки и программируемое поле. В ПЛИС есть фиксированные ресурсы, например, блоки цифровой обработки сигналов и блоки памяти. Но доминирующая логика создается из программируемых логических ячеек. То есть инженер сам определяет архитектуру устройства.

- Гибкость распространяется и на контакты. Для портов ввода-вывода в ПЛИС жестко заданы только физические параметры: количество выводов и их потенциальные электрические характеристики. Например, банк выводов может работать от 1,2 В до 3,3 В. Ключевое слово здесь — потенциальные. Разработчик сам определяет, какой внутренний логический сигнал будет подключен к какому выводу и в каком конкретно режиме (напряжение, скорость, тип линии) этот вывод будет работать.

Чем разработка на ПЛИС отличается от привычного программирования

Чтобы понять эту идею, сравним ПЛИС с тем, что знакомо многим — с микроконтроллером. В МК у вас уже есть готовая аппаратная платформа: ядро (например, Cortex-M), периферия (UART, SPI, таймеры) и фиксированные выводы. Разработчик пишет программу — последовательность инструкций, которая заставляет эту готовую платформу делать что-то полезное. То есть программируется поведение заранее заданного железа.

ПЛИС — это иная парадигма. Здесь вы не управляете готовой платформой, а создаете ее с нуля под конкретную задачу.

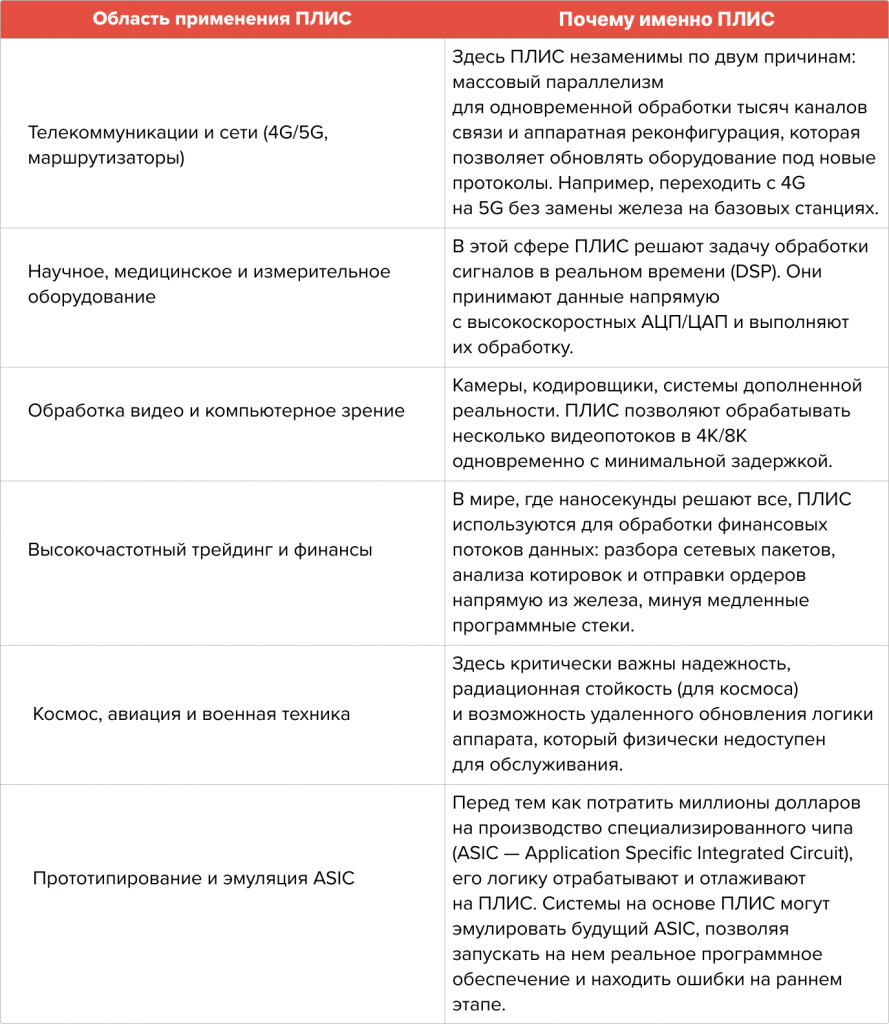

Где применяются ПЛИС

Ниши, в которых важны гибкость и параллелизм ПЛИС:

ПЛИС, микроконтроллеры и ASIC: выбор платформы

Когда перед нами стоит задача создать цифровое устройство, сначала нужно выбрать платформу реализации. Мы можем выбрать ПЛИС, микроконтроллер (МК) или заказать специализированную интегральную схему (ASIC).

Если быть точными, и ПЛИС, и МК — технически тоже ASIC. Поэтому уточню: под ASIC в тексте имею в виду неконфигурируемую микросхему специального назначения, спроектированную под определенную задачу.

И еще одно уточнение: готовые серийные ASIC общего назначения не сопоставляются с ПЛИС напрямую, поскольку не являются альтернативой с точки зрения архитектурного выбора — это законченные компоненты с фиксированной функцией.

Когда выбирают неконфигурируемую схему

ASIC как платформу разработки выбирают в случаях, когда требуется максимальная производительность и энергоэффективность, логика устройства не предполагает изменений после производства, а бюджет проекта позволяет покрыть высокие начальные затраты — например, при планировании массового производства. Также ASIC выбирают, когда нужно защитить интеллектуальную собственность от копирования (повторить микросхему сильно сложнее, чем «украсть» прошивку). Типичные области применения — криптография, высокочастотный трейдинг и массовая потребительская электроника.

Когда выбирают микроконтроллер

Когда предполагается, что логика работы устройства в основном последовательная, основана на стандартных интерфейсах (UART, I2C, USB), не предъявляет жестких требований ко времени отклика (вплоть до наносекунд) и не требует массового параллелизма. А также если критичны низкая стоимость, энергопотребление и скорость разработки.

Когда выбирают ПЛИС

ПЛИС занимают уникальную нишу между двумя вариантами выше:

- В отличие от ASIC, они реконфигурируемы. Это снижает риск и позволяет обновлять устройства.

- В отличие от микроконтроллеров, они позволяют аппаратно реализовывать алгоритмы, чувствительные ко времени, и обеспечивать истинно параллельную обработку множества потоков данных.

Нужно 26 независимых SPI-интерфейсов, работающих одновременно? Или обрабатывать 8 видеопотоков в реальном времени с возможностью обновления логики? Здесь ПЛИС — часто единственный корректный выбор.

На практике эти платформы редко конкурируют, зачастую дополняют друг друга в одной системе. Пример такой системы:

- ПЛИС параллельно собирает данные с быстрых АЦП (покупной ASIC) и первично их обрабатывает (фильтрует, преобразовывает).

- Микроконтроллер или встроенное процессорное ядро выполняет управление, упаковку данных в пакеты, сетевой стек и общее управление системой.

- Внешняя память (RAM, Flash) — покупные ASIC, используемые всеми компонентами.

История появления ПЛИС: от транзистора до FPGA

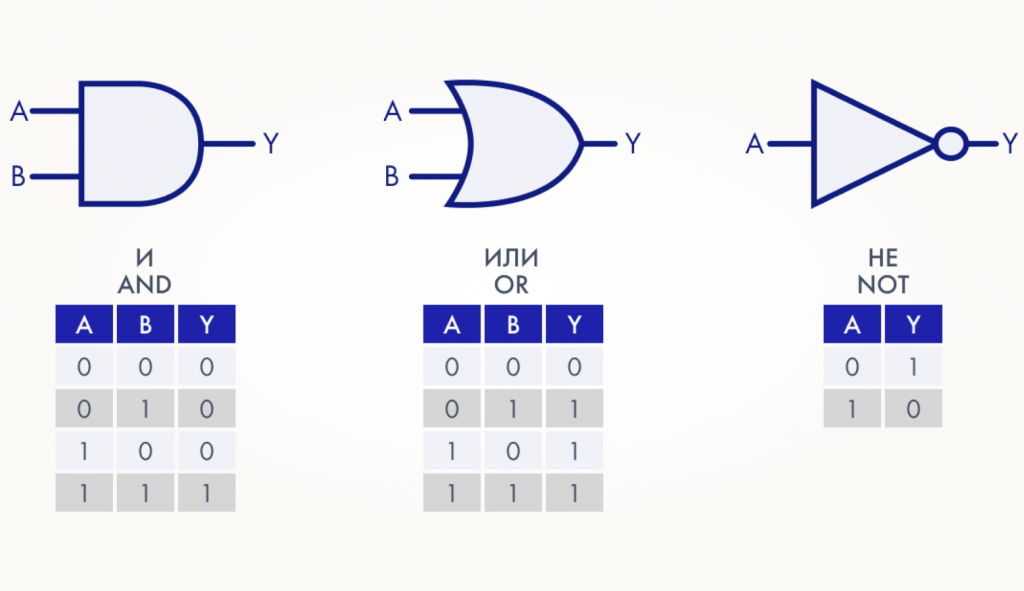

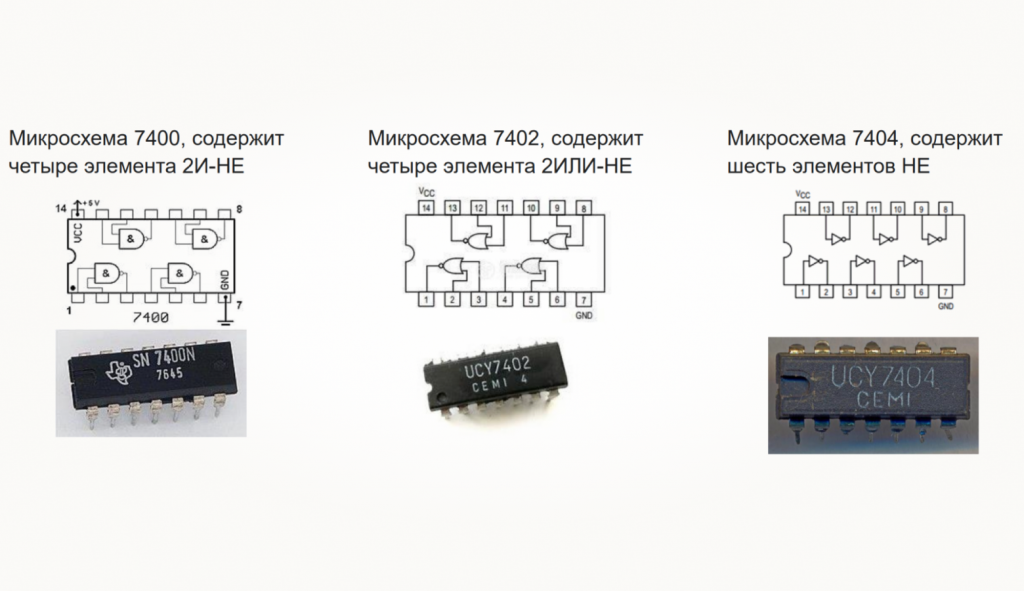

История ПЛИС начинается с изобретения транзистора в 1947 году. Транзисторы позволили реализовать базовые логические элементы «И», «ИЛИ» и «НЕ», из которых можно собрать любую цифровую схему. Более подробно про логические элементы в статье.

Следующим шагом стали микросхемы с готовыми логическими элементами, например, популярная серия 74xx. Чтобы создать сложное устройство, инженеры брали десятки таких микросхем и соединяли их на печатной плате. Этот подход был гибким, но по мере роста сложности проектов стал непрактичным: платы разрастались, увеличивалось энергопотребление, а внесение изменений требовало переразводки и перепайки.

Решением стали первые ПЛУ — программируемые логические устройства:

- PAL (Programmable Array Logic) — программируемая матричная логика, в которой настраивается логическая часть AND, а OR остается фиксированной. Простое и быстрое решение.

- PLA (Programmable Logic Array) — программируемая логическая матрица с возможностью настройки и AND, и OR, что обеспечивает большую гибкость.

- GAL (Generic Array Logic) — универсальная матричная логика, усовершенствованный вариант PAL с возможностью многократного перепрограммирования.

Это дало гибкость, но такие устройства все еще плохо масштабировались.

Следующим этапом развития стали CPLD (Complex Programmable Logic Device) — сложные программируемые логические устройства, состоящие из нескольких логических блоков, объединенных системой программируемых соединений (интерконнектом). Интерконнект обеспечивал связь между блоками, но топология соединений была предопределена на уровне архитектуры чипа в отличие от FPGA, где длина и топология определяются в процессе размещения элементов на кристалле.

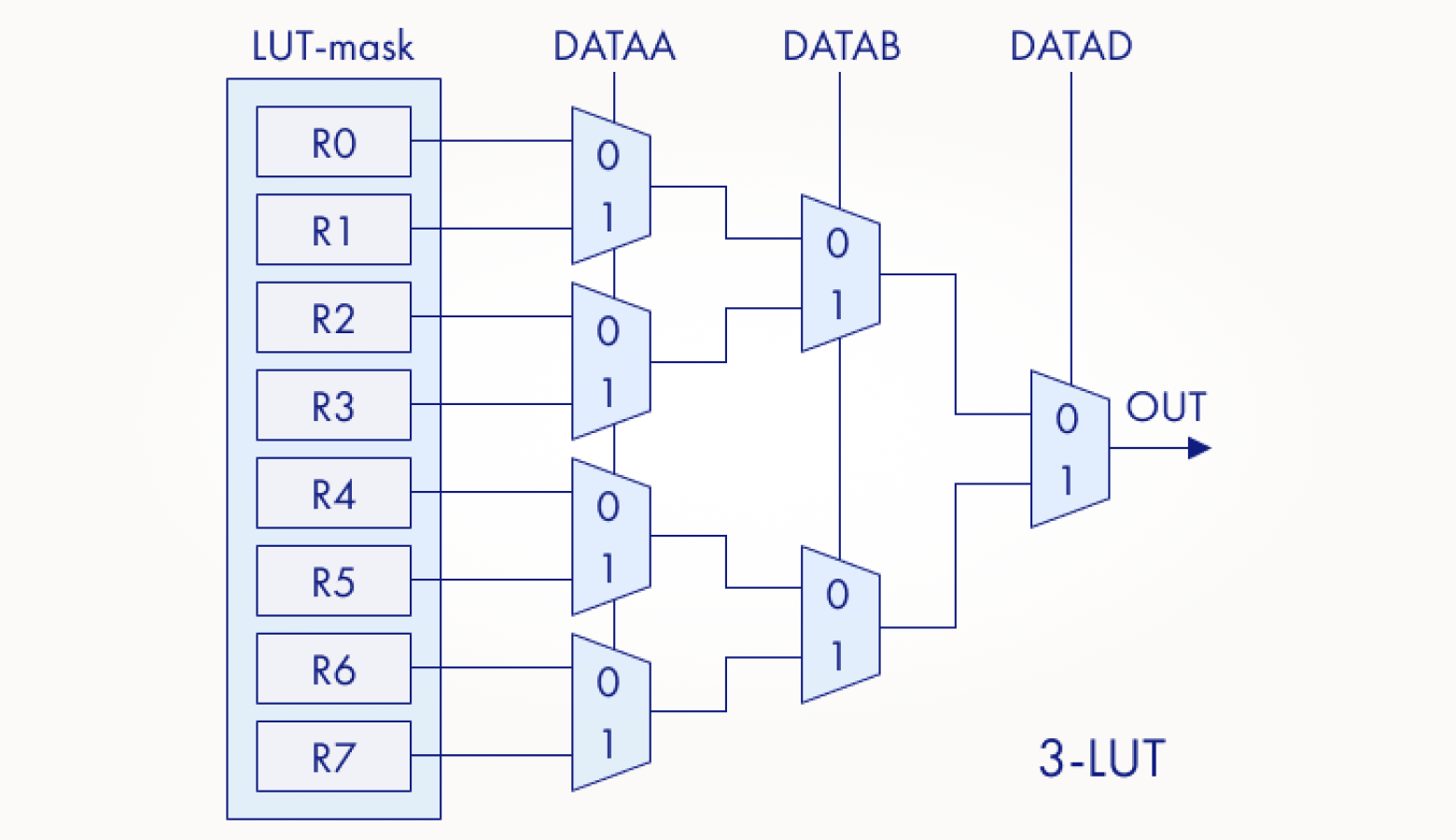

Главным изобретением стала таблица поиска (Look-Up Table, LUT) — программируемый комбинационный блок, который аппаратно реализует произвольную функцию, заданную ее таблицей истинности.

Комбинационная логика (Combinational Logic) — это логика без памяти. Выход такого блока зависит только от текущей комбинации входных сигналов в данный момент времени. Она преобразует данные мгновенно (с учетом небольших задержек). Простые примеры: сумматор (A+B), мультиплексор (выбор одного из входов), дешифратор.

Регистровая логика (Sequential / Registered Logic) — это элементы памяти. В регистрах (триггерах) сохраняется результат работы вычислений, выполненных в комбинационной логике. Данные обновляются по фронту тактового сигнала и хранятся неизменными до следующего фронта.

Вернемся к LUT: в разных источниках термин переводится по разному, например — таблица поиска, таблица соответствия или просмотровая таблица.

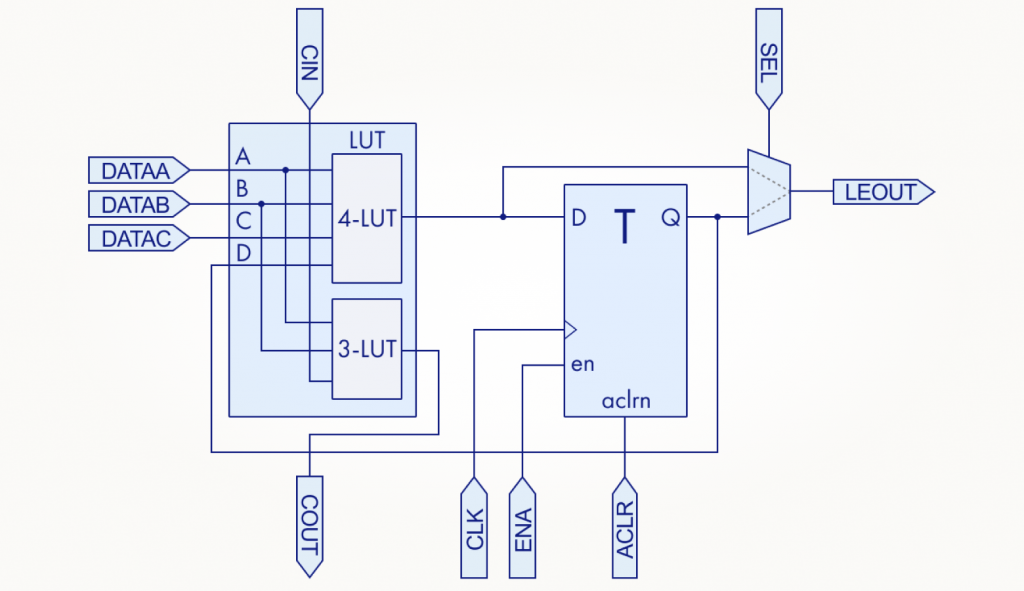

LUT легло в основу программируемых интегральных схем, так первая FPGA появилась в середине 1980-х годов. Базовый элемент такой архитектуры — конфигурируемый логический блок (Configurable Logic Block, CLB) или логический элемент (Logic Element, LE). Именно из множества таких блоков, соединенных программируемой сетью соединений, собирается цифровое устройство.

На рисунке ниже изображен обобщенный вид CLB: две просмотровые таблицы, элемент памяти (D-триггер) и мультиплексор, который определяет выход — комбинационный, то есть реализованный только на логике (выход LUT), или регистровый.

Разобраться в том, как устроены цифровые и аналоговые устройства, помогут книги из подборки «Истового инженера».

Из чего состоит ПЛИС

Теперь разберем, из каких компонентов состоит ПЛИС и как они взаимодействуют друг с другом. Начнем с Lookup Table — базового блока ПЛИС, который хранит заранее заданные логические ответы. А затем разберем, как регистры и триггеры, мультиплексоры, программируемый интерконнект и специализированные блоки делают из этих элементов полноценную схему.

Lookup Table — сердце ПЛИС

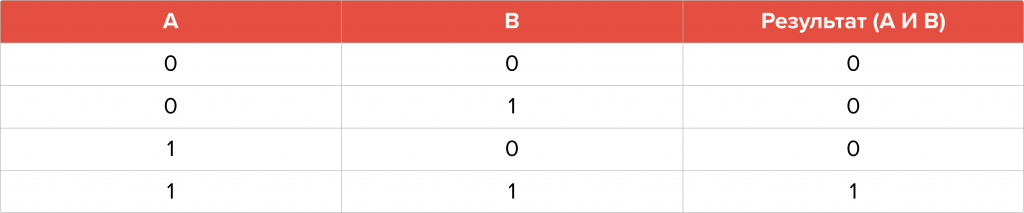

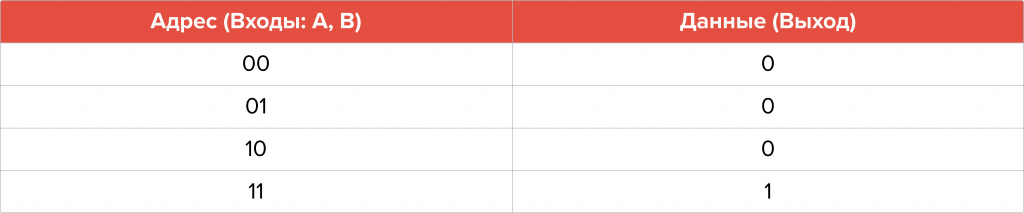

Лучший способ понять принцип работы просмотровой таблицы (LUT) — представить ее как крошечную память с заранее запрограммированными ответами. Возьмем простейшую логическую операцию — «И» (AND). Ее таблица истинности для двух входов (A и B):

Теперь представим, что эта таблица «зашита» в LUT с двумя входами.

- Входы LUT (A и B) — это «адресная шина». Их комбинация указывает на конкретную строку в таблице.

- Выход LUT — это «данные» из этой строки.

Как это работает в реальности: в LUT хранятся эти четыре значения (0, 0, 0, 1) для соответствующих адресов. В момент работы, если на входы поступает A=1, B=1 (адрес 11), LUT мгновенно выдает заранее заготовленный ответ для этого адреса — 1.

Под «памятью» LUT в подавляющем большинстве современных ПЛИС понимают статические RAM-ячейки (SRAM). Они энергозависимы: при выключении питания их конфигурация стирается. Поэтому ПЛИС при каждом старте загружает «таблицы» для всех LUT из внешней энергонезависимой конфигурационной памяти.

LUT не вычисляет результат логической операции в реальном времени. Она хранит все возможные ответы заранее, а входные сигналы лишь указывают, какой из этих готовых ответов нужно выдать. Это и делает LUT идеальным, универсальным и перепрограммируемым «строительным кирпичиком» для цифрового мира ПЛИС.

Регистры

Сам по себе LUT реализует логическое преобразование (комбинационную логику) — его выход меняется сразу при изменении входов (с учетом небольших задержек). Однако для реализации сложных схем нужно сохранять результаты, передавать их между блоками и синхронизировать работу.

Для этого каждый вычислительный блок (CLB) в ПЛИС содержит не только LUT, но и регистр (триггер). Их роли четко разделены:

- LUT (комбинационная логика): вычисляет логическую функцию без привязки к тактовому сигналу.

- Регистр (память): запоминает выход LUT в момент прихода тактового импульса и хранит это значение неизменным до следующего такта.

Регистр — это «хранитель», дисциплинированный тактовым сигналом. Вместе они образуют элементарную ячейку любой синхронной цифровой системы в ПЛИС.

Мультиплексоры и режимы работы

Гибкость конфигурируемого логического блока (CLB) обеспечивается, в том числе, внутренними мультиплексорами (MUX). Их задача — выбрать для выхода логического блока источник сигнала.

Как это работает:

- Мультиплексор — это цифровой переключатель с одним выходом и несколькими входами. Управляющий сигнал мультиплексора указывает ему, с какого именно входа передавать данные на его единственный выход.

- Внутри CLB такие мультиплексоры решают, например, будет ли на выход блока подаваться прямое значение с LUT или зафиксированное значение с регистра.

- За пределы блока сигнал с выхода мультиплексора (и всего CLB) попадает в глобальную программируемую сеть соединений (программируемый интерконнект, routing). Эта сеть — отдельный и сложный ресурс ПЛИС, который отвечает уже за маршрутизацию сигналов между разными блоками и определяет, куда именно этот сигнал будет передан.

Программируемость в ПЛИС иерархична:

- Уровень блока (CLB): мультиплексоры выбирают, откуда брать сигнал (из LUT или регистра).

- Уровень кристалла: сеть соединений определяет, куда передать этот сигнал (к какому другому блоку или на выход микросхемы).

Такая архитектура позволяет реализовывать разные цифровые схемы на одной и той же платформе.

Программируемый интерконнект

Отдельно стоит поговорить о том, что соединяет все эти блоки между собой. В ПЛИС нет фиксированных проводников, как в специализированных микросхемах (ASIC).

Вместо фиксированных проводников используется программируемая матрица интерконнекта — сложная сеть готовых проводящих линий (каналов) и программируемых электронных переключателей (ключей), которая настраивается при каждой «прошивке».

Интерконнект определяет:

- как логические блоки (CLB) связаны друг с другом,

- по каким путям идут сигналы по кристаллу,

- какие задержки возникают при передаче сигнала от одного элемента к другому.

По сути, когда мы прошиваем ПЛИС, мы программируем не только логику внутри блоков (LUT, триггеры), но и всю физическую конфигурацию соединений между ними. Мы «замыкаем» нужные переключатели в интерконнекте, формируя необходимые проводящие пути. То есть фактически создаем нужную нам схему соединений на кристалле.

Специализированные блоки

Современные ПЛИС давно перестали быть только набором LUT и регистров. Внутри кристалла обычно есть и более крупные, специализированные компоненты:

- Блоки памяти (BRAM).

- DSP-блоки (блоки ЦОС) — аппаратные вычислители, высокоскоростные интерфейсы.

- Аппаратно-реализованные интерфейсы — высокоскоростные трансиверы, шины.

Устройства, в которых аппаратно реализованы интерфейсы, ускорители и процессорные ядра, производители ПЛИС выделяют в отдельный класс — системы на кристалле (SoC, System-on-Chip). - Встроенные процессорные ядра, заложенные на аппаратном уровне.

Помимо логики и специализированных блоков, В ПЛИС можно реализовывать процессорные ядра, создаваемые из программируемых ресурсов кристаллов (soft-процессоры).

Архитектурное разнообразие ПЛИС, от состава базового логического элемента до набора специализированных блоков, напрямую определяет сферу применения и цену кристалла. Поэтому критически важно определять необходимую микросхему на ранних этапах проектирования. Неверный выбор грозит двумя рисками:

- «Не влезть» в выбранную ПЛИС, например когда для алгоритма не хватает DSP-блоков или памяти, и он не может работать на требуемой скорости. Использование более 80% ресурсов ПЛИС приводит к сложностям размещения, разводки и выполнения временных ограничений.

- Серьезно переплатить за слишком мощную и дорогую ПЛИС, ресурсы которой останутся неиспользованными, а также усложнить систему питания и охлаждения без необходимости.

Почему разработка на ПЛИС — это не программирование, а проектирование аппаратуры

Выше я писала, что при работе с ПЛИС платформу нужно спроектировать самостоятельно под конкретную задачу, и теперь рассмотрю главные отличия от программирования. Мы часто говорим «запрограммировать ПЛИС», имея в виду загрузку конфигурационного файла в память микросхемы. Человека, который создает такую конфигурацию, тоже могут назвать программистом. Но технически это не совсем верно. В чем же принципиальная разница?

Классическое программирование — это написание последовательности команд для процессора. Неважно, идет ли речь о языке C для микроконтроллера или об объектно-ориентированном Java для сервера. Все в итоге сводится к инструкциям, которые ядро исполняет одну за другой во времени. Даже если внутри есть конвейеры и несколько ядер, модель мышления остается линейной.

Разработка для ПЛИС — это проектирование цифровой схемы. Мы не пишем команды, а описываем структуру будущего устройства:

- какие логические блоки существуют,

- какие сигналы между ними идут,

- где хранятся данные,

- по какому такту все синхронизировано.

Код в ПЛИС не исполняется, он синтезируется в схему, которая затем размещается и трассируется на кристалле. В момент загрузки конфигурационного файла в ПЛИС возникает спроектированное цифровое устройство.

Ниже — два главных отличия проектирования на ПЛИС от привычного понимания программирования.

Параллельность по умолчанию

В классическом программировании команды выполняются последовательно. Параллельность может быть условна, как в диспетчере задач ОС реального времени, который переключает контекст, либо ограничена конкретным числом потоков или физических ядер процессора.

В ПЛИС все наоборот: параллельность процессов — состояние по умолчанию, чтобы организовать последовательные вычисления нужно явно это указать. Например когда операция B должна дождаться результата A, необходимо заложить такую логику в описание: реализовать флаг готовности, сконструировать конечный автомат (FSM), организовать обмен данными и так далее.

Из-за этого многие алгоритмы, которые для процессора выглядят тяжелыми, на ПЛИС реализуются естественно и эффективно (и наоборот).

Время — часть логики

Еще одно ключевое отличие от программирования — отношение ко времени:

- Программируя микроконтроллер или разрабатывая ПО верхнего уровня, мы работаем с готовой, фиксированной аппаратной архитектурой. Тактовый генератор, шины, периферия — все это уже спроектировано, отлажено и гарантированно работает на заданной частоте. Наша задача — написать код, который корректно использует эти готовые временные интервалы. Например, выдерживая паузы для шины данных. Мы не можем и не должны менять задержки внутри процессора, они заданы производителем.

- Проектируя систему на ПЛИС, мы создаем аппаратную архитектуру с нуля. Мы сами определяем, как будут соединены логические элементы, и мы отвечаем за то, чтобы созданные нами пути успевали передавать сигналы между регистрами за один такт. Здесь время — не внешнее условие, а неотъемлемая часть нашей логики. Можно написать идеальный с точки зрения функций код, но если нарушены временные ограничения (timing constraints) — схема будет работать нестабильно или не заработает вообще.

Языки для проектирования на ПЛИС

Для разработки на ПЛИС используются языки описания аппаратуры — HDL (Hardware Description Language). Например, Verilog, VHDL, System Verilog. Немного о каждом:

- Verilog — компактный, лаконичный, конструкции напоминают C.

- VHDL — более строгий и формальный, с явной типизацией.

- System Verilog — основан на языке Verilog, использует принципы ООП, незаменим в сфере верификации.

Языки-помощники: автоматизация и управление

Разработка современной сложной системы на ПЛИС — это не только написание HDL-кода. Это еще и управление проектом, автоматизация и работа с высокоуровневыми моделями. Здесь на помощь приходят другие языки.

Языки высокоуровневого синтеза (HLS). Они позволяют описать алгоритм на C, C++, а затем автоматически сгенерировать из него оптимизированное RTL-описание для ПЛИС. Это ускоряет прототипирование сложных вычислительных блоков.

Скриптовые языки для автоматизации. Tcl (Tool Command Language) — это «язык общения» со средствами САПР. С его помощью пишут скрипты для автоматизации рутинных задач: создания проекта, запуска синтеза и анализа результатов и задают временные и физические ограничения (constraints).

Python активно используют для создания сложных инфраструктурных скриптов, предварительной обработки данных, управления репозиториями и интеграции разных инструментов в единый пайплайн.

Генерация HDL из моделей (MATLAB/Simulink). Для алгоритмов обработки сигналов и систем управления часто сначала создают и отлаживают математический алгоритм в MATLAB & Simulink. С помощью специальных пакетов (HDL Coder) эту исполняемую модель можно напрямую преобразовать в HDL-код, что гарантирует соответствие модели и реализации.

Модуль как базовый строительный блок

Основная структурная единица в проекте на ПЛИС — это модуль. Его можно мысленно представить как готовую цифровую микросхему на виртуальной печатной плате. У него есть «ножки» — то есть порты для ввода/вывода сигналов и шин, внутренняя логика и строго определенная функция.

Проекты ПЛИС строятся по принципу иерархичности:

- Вы проектируете или берете из библиотек простые, отлаженные «микросхемы» — модули: счетчики, декодеры, FIFO, контроллеры интерфейсов.

- Затем встраиваете их в модули более высокого уровня, соединяя порты, как дорожки на плате.

- Так получается иерархия проекта: модуль верхнего уровня (top-файл), который описывает всю систему и содержит несколько подмодулей, каждый из которых может содержать свои подмодули.

У модульного подхода есть ряд преимуществ:

- Повторное использование (Reusability). Один раз отлаженный модуль можно многократно использовать в десятках проектов, просто подключив его. Это экономит время и сводит к нулю риск ошибок в этой части логики.

- Упрощение отладки и верификации. Модуль можно протестировать изолированно, до интеграции в большую систему.

- Масштабируемость и читаемость. Сложную систему, разбитую на логические блоки с четкими интерфейсами, намного легче понять, модифицировать и поддерживать, чем гигантский монолитный файл кода.

САПР в работе: путь от RTL-кода до цифрового устройства в ПЛИС

Процесс проектирования устройства на ПЛИС начинается с описания на HDL. После этого САПР последовательно преобразует это описание в конфигурацию кристалла. Этот путь включает три ключевых этапа.

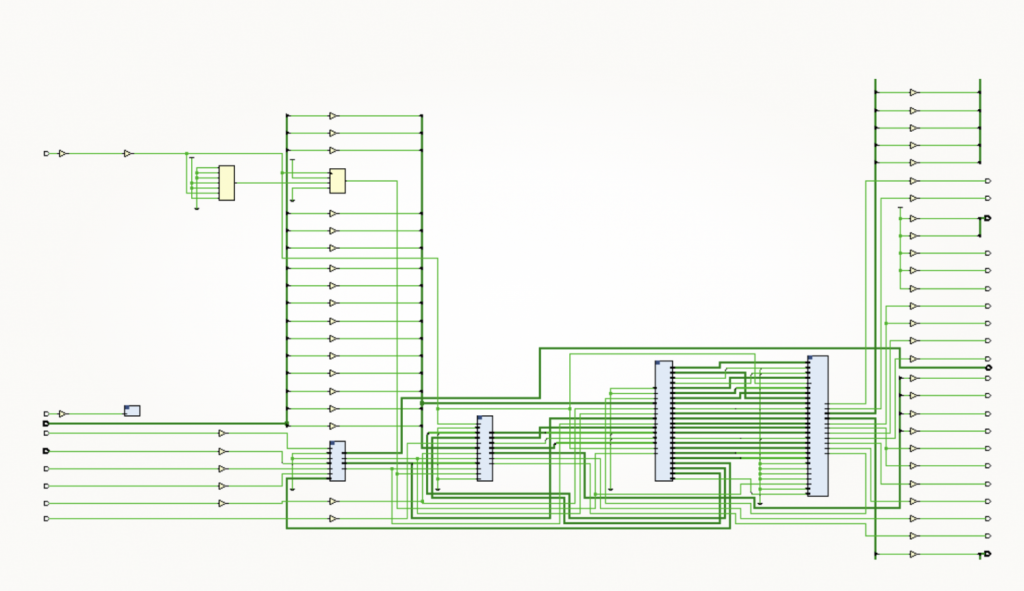

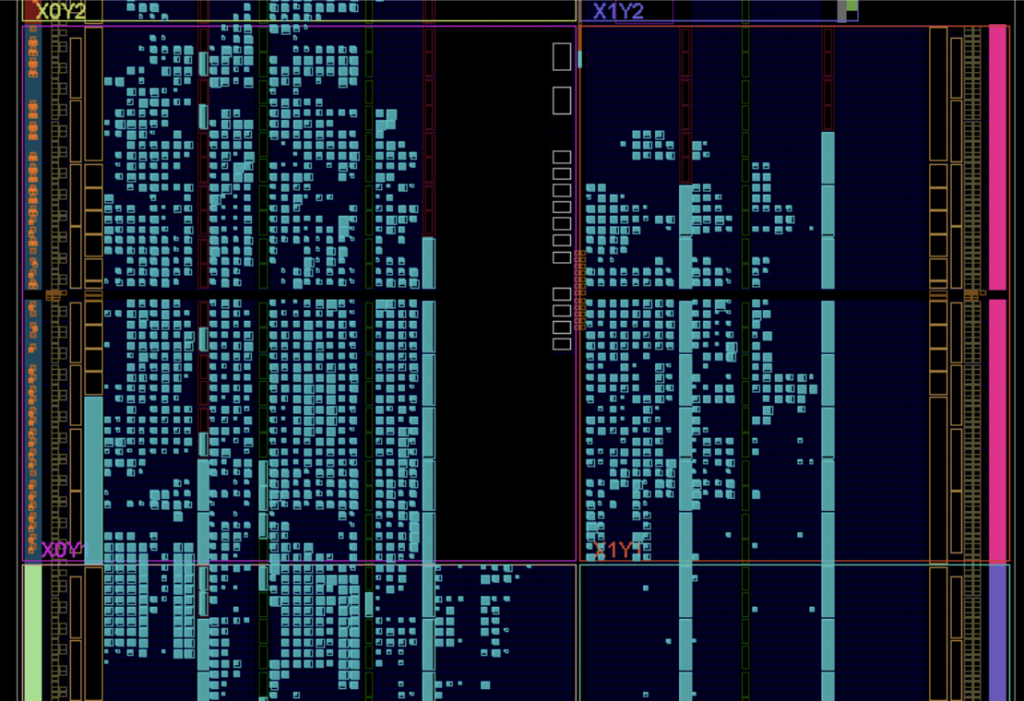

Первый этап — синтез (Synthesis), то есть создание «чертежа» схемы. САПР преобразовывает HDL-код в логическую схему, пригодную для аппаратной реализации в ПЛИС. Синтезатор анализирует описание аппаратуры на языке HDL и определяет, какие элементы схемы должны быть реализованы в виде комбинаторной логики, регистров и связей между ними. Результаты работы синтезатора — нетлист (netlist), список примитивов и цепей.

Второй этап — имплементация (Implementation), то есть «разводка» схемы на кристалле. Имплементацию делают в два этапа: размещение (Placement) и трассировка (Routing). На этапе размещения САПР решает, где именно на кристалле будут находиться логические элементы, стараясь минимизировать задержки и уложиться в заданные частоты и ограничения.

После размещения выполняется трассировка. САПР рассчитывает соединения между элементами так, чтобы уложиться в требуемые характеристики.

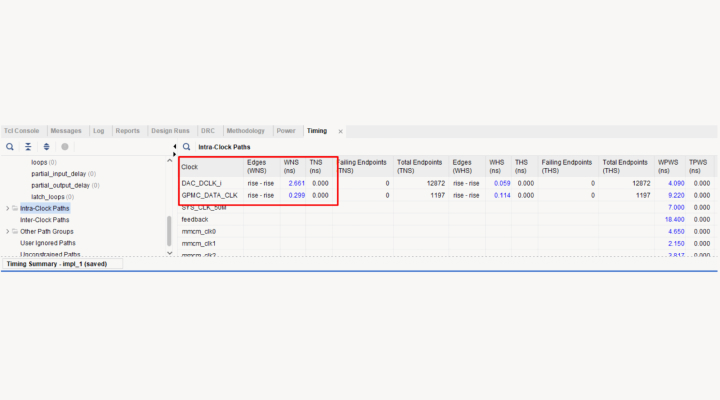

По результатам имплементации САПР производит временной анализ, STA (static timing analysis). САПР производит его и генерирует отчет после размещения элементов и соединений между ними. В отчете можно увидеть, удалось ли уложиться в заданные временнЫе характеристики или «тайминги». Более подробно о них — в следующем разделе.

Результат всех этапов — генерация файла конфигурации, или битстрим (bitstream), который загружается в ПЛИС. В этот момент код окончательно реализуется в железе.

Тайминги и физика: самая коварная часть проектирования на ПЛИС

На этом этапе начинается самое интересное и сложное. Проектирование на ПЛИС — это в первую очередь создание надежных цифровых схем. Основу этого процесса составляет синхронный дизайн — подход, при котором жизненный цикл данных жестко привязан к тактовому сигналу. Данные между тактами изменяются комбинационной логикой, а регистры фиксируют новые значения по такту.

Сигнал в ПЛИС распространяется не мгновенно. Задержки вносят LUT, проводники интерконнекта и сами триггеры. Главная задача — уложить все вычисления на пути между двумя регистрами в один такт.

Что будет если пренебречь принципами синхронного дизайна

Может быть, ничего. А может, регистр защелкнет значение слишком рано или слишком поздно или схема «улетит» в неизвестное состояние из-за метастабильности. Ошибки синхронного проектирования — самые коварные, они могут не сразу проявиться внешне. Например, устройство будет будет вести себя по-разному в разных условиях, — работать «на столе», но перестанет при нагреве или охлаждении.

Ниже — пять особенностей синхронного дизайна, на которые стоить обращать внимание при проектировании на ПЛИС.

1. Долгий путь между регистрами

Обычно у проекта на ПЛИС задана целевая тактовая частота, например 100 МГц (в системе их может быть несколько, но для простоты рассмотрим одну). После этапа имплементации САПР выполняет временной анализ и сообщает максимальную частоту, на которой схема может корректно работать. Если рассчитанная частота оказывается ниже требуемой, проект необходимо дорабатывать.

Поскольку частота обратно пропорциональна периоду тактового сигнала, увеличение частоты означает уменьшение периода. Все регистры внутри одного тактового домена работают на одной и той же частоте. Поэтому достаточно, чтобы хотя бы один путь между регистрами превышал допустимую задержку, — и именно он ограничит максимальную частоту всей схемы.

Самый длинный путь между регистрами в схеме называется критическим путем. Его длина определяет максимальную частоту (Fmax) работы вашей логики. Если заданная частота выше максимальной — схема не будет стабильна.

Если САПР сообщает, что Fmax ниже требуемой, есть несколько вариантов решения:

- Конвейеризация (Pipelining). Можно разбить длинную логическую цепочку на несколько этапов с добавлением промежуточных регистров. Это увеличивает задержку (latency), но резко повышает частоту.

- Упрощение логики. Переписывание алгоритма для уменьшения количества последовательных операций.

- Ресинтез с другими стратегиями. Указание САПР оптимизировать схему либо для скорости (Performance), либо для площади (Area).

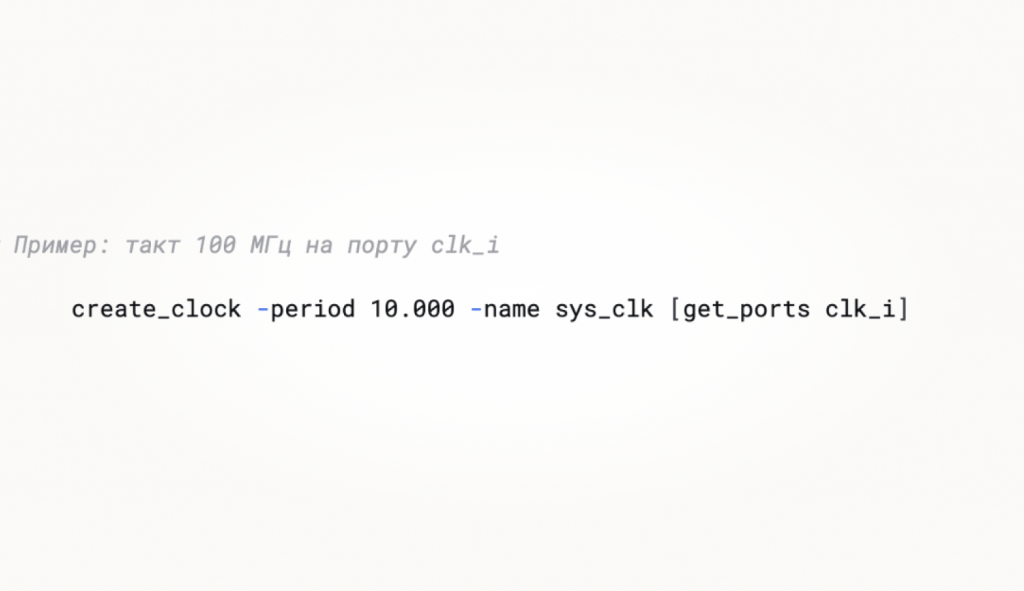

Как задавать временные ограничения для САПР

Для этого нам нужен специальный файл — timing constraints file. В нем содержатся технические требования, которые синтезатор и инструменты размещения/трассировки обязаны выполнить.Чтобы «прописать констрейнты», то есть задать временные ограничения, используют специализированный скриптовый язык ограничений (Tcl-based), который понятен инструментам.

- Определение тактовых сигналов

(create_clock). Вы указываете САПР, какой сигнал является тактовым, его период (частоту), форму и источник. - Ограничения на ввод/вывод

(set_input_delay, set_output_delay). Задают задержку распространения входного/выходного сигнала относительно тактового сигнала на интерфейсе проекта - Ложные пути

(set_false_path). Вы явно указываете САПР, что определенные логические пути — например, между независимыми тактовыми доменами, которые синхронизируются через FIFO, не нужно проверять и оптимизировать на предмет временных нарушений. Это предотвращает бессмысленную трату ресурсов САПР и ложные ошибки. - Мультицикловые пути

(set_multicycle_path). Вы даете САПР явное разрешение на то, что определенной логической операции (например, сложному вычислению) разрешено занимать более одного тактового цикла. Это инструмент для осознанного «ослабления» требований к некритичным по скорости частям схемы, чтобы сосредоточить усилия САПР на действительно важных путях.

2. Пунктуальность регистра до наносекунд

В синхронной логике данные триггера не должны меняться в определенном временном промежутке до и после прихода тактового импульса. Такие временные параметры называются временем предустановки и временем удержания (Tsetup и Thold). Эти параметры САПР учитывает в своих расчетах.

Именно изменение данных в недопустимом временном окне приводит к метастабильности.

По результатам размещения и трассировки САПР предоставляет отчет: удалось ли уложиться заданные временные характеристики и показывает запас по времени.

3. Разные домены тактовых частот

Любая система, где есть несколько тактовых сигналов, сталкивается с проблемой передачи данных между разными тактовыми доменами (Clock Domain Crossing, CDC). Если данные между регистрами разных тактовых доменов передавать напрямую, то мы нарушим принцип синхронного дизайна: передающий и принимающий регистр будут работать по разному тактирующему импульсу.

Поэтому в такой ситуации используются различные способы синхронизации тактовых доменов, например, простой синхронизатор на триггерах или FIFO.

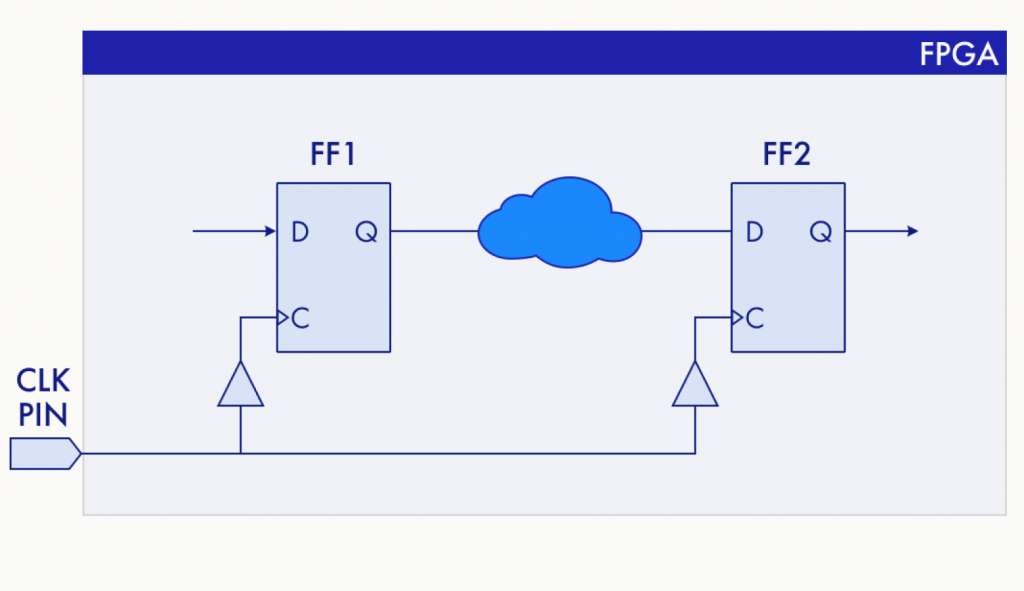

- Синхронизаторы. Самый простой метод — использование цепи из двух (или более) последовательных триггеров, тактируемых целевым тактом. Это не предотвращает метастабильность в первом триггере, но экспоненциально снижает вероятность ее распространения дальше в систему.

- Буферные структуры. Для передачи потоков данных используют асинхронные FIFO. Они изолируют домены друг от друга, обеспечивая безопасную передачу с сохранением порядка данных.

По сути, даже применяя правило синхронного дизайна, мы не можем полностью избавиться от этого явления, а делаем вероятность его возникновения ничтожно малой.

4. Асинхронные сигналы

Работа с сигналами, которые не синхронизированы с тактовым доменом — например, кнопка сброса, флаг прерывания от внешнего устройства, — особая и обязательная тема в синхронном дизайне.

Прямое подключение внешнего сигнала сброса (rst_n) к триггерам без синхронизации создает две проблемы:

- Нарушение требований снятия (Removal Time) и восстановления (Recovery Time). Это временные требования триггера к сигналу сброса, аналогичные setup/hold для данных. Если сброс снят слишком близко к тактовому фронту, часть триггеров может выйти из сброса в этом такте, а часть — в следующем. Система окажется в несогласованном состоянии.

- Метастабильность. Если асинхронный сигнал изменится непосредственно в момент выборки регистром (в окне setup/hold), его значение может привести к метастабильности в цепочке логики или быть воспринято неправильно.

Чтобы избежать этих проблем, любой внешний асинхронный сигнал, включая сброс, должен быть синхронизирован с тактовым доменом, в котором он используется. Для этого применяются цепи синхронизации.

5. Защелки

Защелки — это регистры, которые работают не по тактовому сигналу, а по изменению разрешающего сигнала. Такие регистры выбиваются из общей картины синхронности.

Как правило защелки появляются в дизайне без намерения автора дизайна, и САПР может указать наличие таких защелок среди предупреждений. Чтобы избежать их появления, нужно явно указывать состояния сигналов во всех возможных состояниях для if-else и case.

Это лишь малая часть тонкостей, которые нужно учитывать при разработке на ПЛИС. Мастерство разработчика проявляется не только в умении описать алгоритм, но и в понимании физики цифровой схемы и методов обеспечения ее надежности.

Проверка устройства: верификация, отладка, тестирование

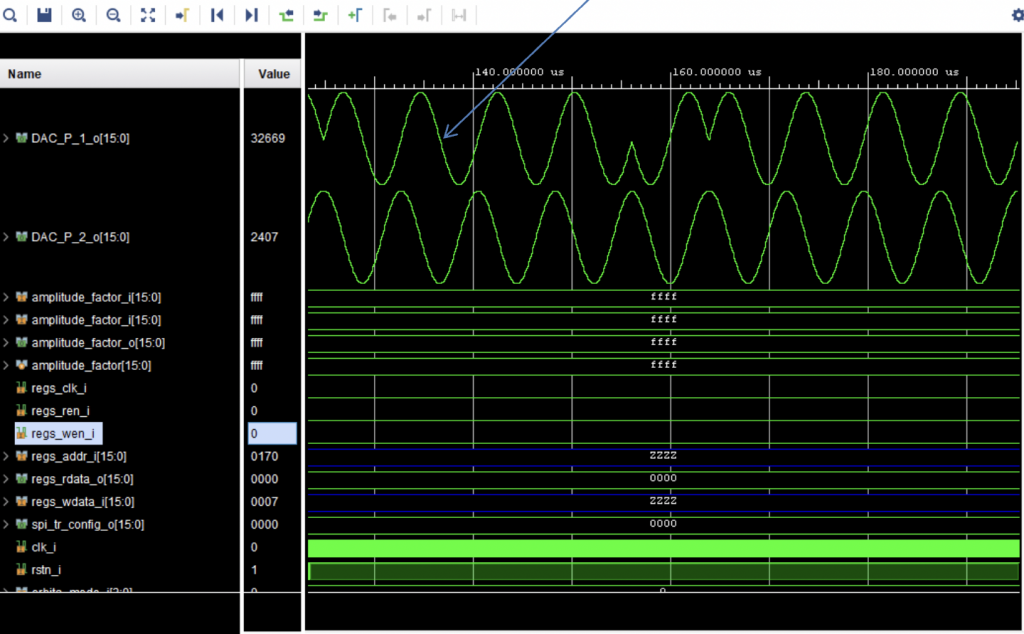

Верифицировать дизайн — значит доказать, что этот разработанное устройство делает именно то, что задумано, и ничего лишнего. Один из главных инструментов на этом этапе — моделирование, оно позволяет проверить работу логики без реального железа.

Затем приступаем к тестированию. На этом этапе уже верифицированный дизайн прошивается в реальную ПЛИС на плате и проверяется работа всей системы целиком: самой ПЛИС, памяти, датчиков и других компонентов.

На всех этапах производится отладка: анализируются логи и сигналы в симуляторе, осциллограммы в реальном железе, внутри ПЛИС и на плате, проводятся дополнительные тесты, чтобы найти и исправить «корень зла».

Теперь рассмотрим более подробно каждый этап.

Моделирование

Это первый и самый важный этап, цель которого — найти и исправить логические ошибки в виртуальной среде, до загрузки кода в реальную ПЛИС. Исправление на этом этапе стоит минимально дешево по времени и ресурсам. Инструменты, которые используют на этом этапе:

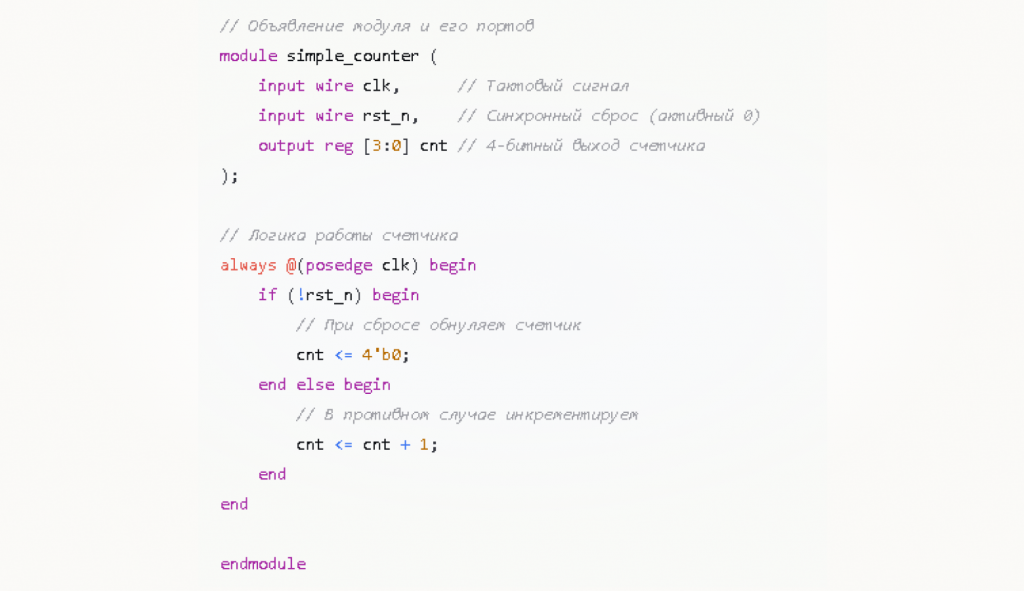

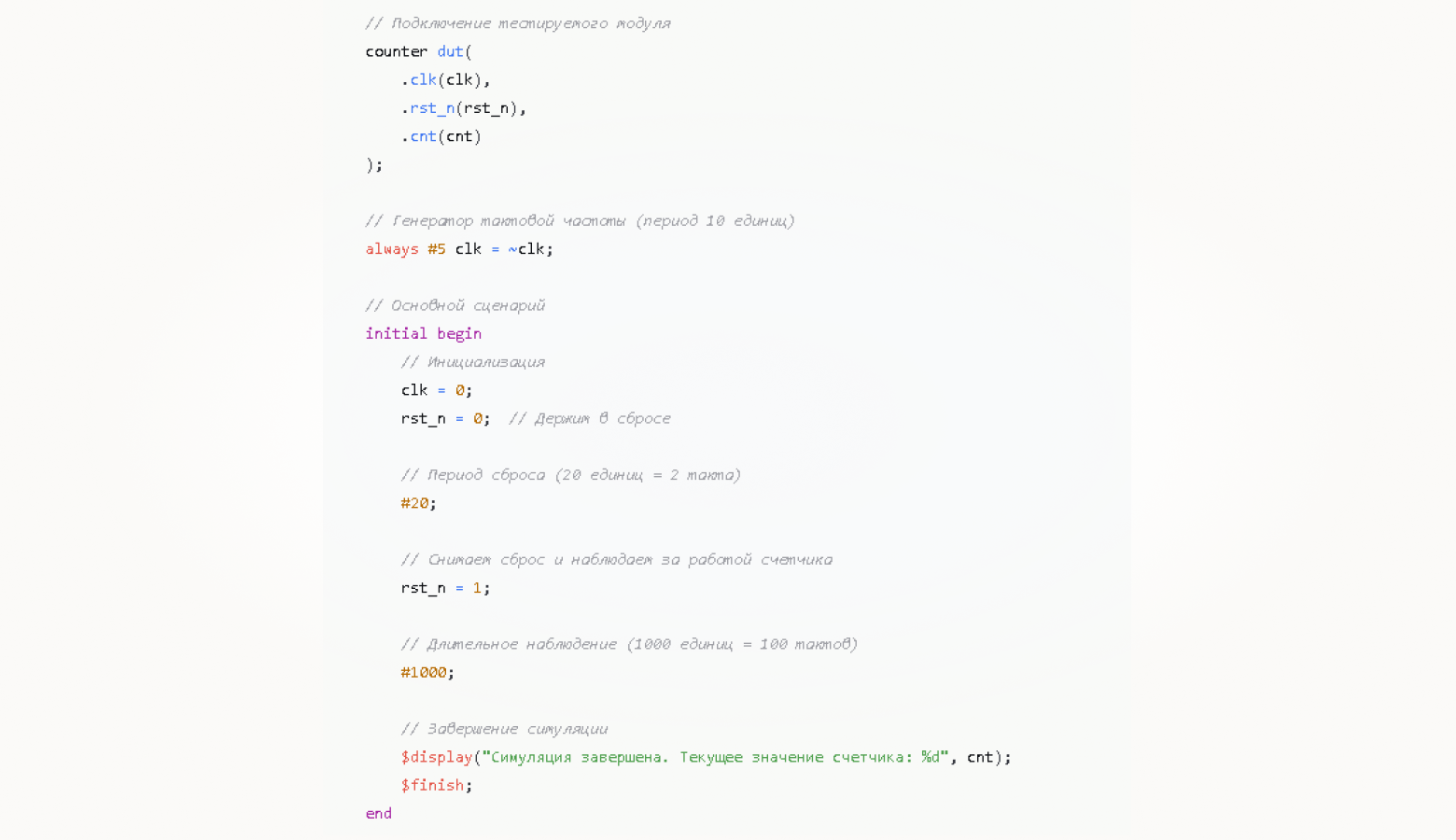

Тестбенч (Testbench). Это специальный HDL-модуль, который имитирует окружение вашего проектируемого устройства (DUT — Design Under Test). Он генерирует тестовые воздействия (сигналы, данные) и автоматически проверяет (если это заложено), соответствуют ли выходные сигналы DUT ожидаемым значениям.

Пример самого простого тестбенча на языке Verilog для счетчика представлен ниже. Он только подает входные воздействия, а результат его работы нужно анализировать «глазами», то есть проверить работоспособность, посмотрев на временные диаграммы (waveform).

В тестбенчах обычно используется более автоматизированный подход: чтение из файла и запись в файл, автоматизированное сравнение с референсом, генерация рандомизированных тестовых данных, вывод в консоль и так далее.

Отладка на плате: заглянуть внутрь кристалла

После успешного моделирования и «прошивки» битстрима в реальную ПЛИС начинается аппаратная отладка. Здесь на помощь приходит встроенный логический анализатор. Это специальное отладочное ядро, которое вы добавляете в свой проект до имплементации. После загрузки конфигурационного файла оно позволяет захватывать и просматривать внутренние сигналы ПЛИС в реальном времени, как цифровой осциллограф.

Верификация

Для верифицирования в сфере проектирования цифровых устройств есть немало средств. Простой тестбенч и анализ временных диаграмм, умение запустить логический анализатор в железе — это самое начало пути. Кратко рассмотрим, что еще существует в мире верификации:

Формальная верификация (Formal Verification). Этот метод математически доказывает или опровергает заданные свойства (утверждения) для всех возможных входных комбинаций и состояний системы.

Утверждения (Assertions). Это формальные правила, встроенные прямо в код (например, на SystemVerilog Assertions, SVA), которые описывают, как система должна себя вести, например: сигнал A всегда должен следовать за сигналом B в течение двух тактов. Во время симуляции эти правила проверяются автоматически, мгновенно сигнализируя о любом нарушении.

Анализ покрытия (Coverage Analysis): Этот процесс отвечает на вопрос: «Насколько тщательно мы проверили свой код?». Специальные инструменты собирают метрики во время симуляции:

- Покрытие кода (Code Coverage). Какая доля строк, ветвей (if-else) и условий (case) кода была выполнена.

- Функциональное покрытие (Functional Coverage): Какая доля запланированных сценариев и комбинаций входных данных была проверена.

Методологии верификации (Verification Methodologies). Для структурирования сложного процесса верификации созданы готовые методологии и библиотеки классов. Например, Universal Verification Methodology (UVM) на базе SystemVerilog. Они предоставляют готовые архитектурные решения для создания модульных, повторно используемых и автоматизированных тестовых сред.

Освоение этих инструментов — естественный путь роста для инженера ПЛИС. Они позволяют перейти от реактивной отладки («почему не работает?») к проактивной верификации («докажем, что работает правильно во всех случаях»).

Кто же такой ПЛИС-инженер и какими навыками он должен обладать

Теперь, когда вы узнали, что такое ПЛИС, из чего она состоит, как проектируется и проверяется, у вас может возникнуть логичный вопрос: а кто всем этим занимается? Кто пишет HDL-код, «сводит тайминги», отлаживает сигналы внутри кристалла и понимает, почему схема «почти работает»? Таких специалистов называют ПЛИС-инженерами, FPGA-инженерами, разработчиками ПЛИС.

Он сразу задает себе вопросы: где здесь регистр, а где комбинационная логика? Что происходит между тактами? Какой путь станет критическим? Что будет, если сигнал придет асинхронно?

Обязательные навыки ПЛИС-инженера:

- Писать и читать HDL-код.

- Строить архитектуру проекта.

- Работать с временными ограничениями.

- Использовать моделирование и отладку.

- Разбираться в интерфейсах и протоколах.

- Понимать цифровую схемотехнику: как код превращается в физическую схему.

Кроме того, ПЛИС-инженеру желательно уметь читать электрические схемы и работать с микроконтроллерами, процессорными ядрами и аппаратурой — например, с осциллографом и анализатором спектра.

ПЛИС — это отдельный класс инструментов со своей философией, сильными и слабыми сторонами. Вопрос стоит не «что лучше», а «что оптимально для каждой части задачи». Грамотный инженер проектирует систему, используя сильные стороны каждой платформы: быстродействие и параллелизм ПЛИС, гибкость и доступность ПО для МК и абсолютную эффективность ASIC для массовых и неизменных функций.

Что еще почитать начинающему ПЛИС-инженеру

- Харрис и Харрис, «Цифровая схемотехника». Одна из лучших книг для будущих инженеров ПЛИС: логика, архитектура, CMOS. В ней простым языком объяснены уровни абстракции цифровых устройств и математические основы, которые я не рассматривала в статье.

- Максфилд Клайв, «Проектирование на ПЛИС. Архитектура, средства и методы. Курс молодого бойца». Книга легко читается даже на начальном уровне и позволяет глубже вникнуть в суть ПЛИС.

- Michael Ciletti — «Advanced Digital Design with the Verilog HDL». Более глубокое и обстоятельное изучение языков для проектирования ПЛИС.

- FPGA-systems — сайт с полезными статьями, новостями и видео. Здесь можно следить за событиями, общаться с участниками и читать понятные руководства: от временных ограничений и сбросов до создания проектов с нуля и работы с интерфейсом SPI.