RnD-цикл современных ASIC/SoC глазами тополога

с помощью нейросети

Илья Пеплов из команды физического дизайна дивизиона полупроводников YADRO рассказал про разработку современных микросхем с фокусом на этап проектирования топологии, объяснил, что такое SoC (System-on-Chip, cистема на кристалле) и как их проектируют в команде Ильи.

- какие этапы можно выделить в создании современных микросхем

- какие команды реализуют их

- как эти команды взаимодействуют друг с другом

- что можно почитать, чтобы узнать больше о дизайне микросхем

- что будет на SoC-хакатоне YADRO

Как разрабатывают микросхемы сегодня

RnD-цикл (Research and Development) разработки микросхем, будь это ASIC или SoC (и даже отчасти FPGA), содержит много трудоемких этапов, где задействовано около десяти команд инженеров. Отдельные фазы RnD-цикла следуют друг за другом, но при этом частично пересекаются. Я разбил цикл на шесть больших этапов, постараюсь не увязнуть в их деталях при их описании.

Весь процесс от начала до момента отгрузки готового продукта занимает в среднем два года. На первом этапе определяют и прорабатывают идею будущей микросхемы. Если речь идет о коммерческом решении, дополнительно прогнозируется интерес и потребности рынка примерно через два года. Проводится расчет экономики проекта.

Далее идея конкретизируется и становится концептом. С ним начинают работать архитекторы, они определяют конечный функционал будущей SoC, что будет входить в ее состав: сколько и каких ядер CPU/GPU, какие IP-блоки различных интерфейсов, внутрикристальные шины и пр. В процессе архитекторы создают высокоуровневую модель SoC — например, с помощью C++ и специального софта.

По мере готовности концепта в дело вступают фронтенд-инженеры — не путайте с фронтендами в вебе. Они создают RTL-описание аппаратуры (RTL, register transfer level — уровень регистровых передач) на HDL-языке, обычно на SystemVerilog. Он позволяет очень точно описать работу сложных логических устройств на функциональном уровне. Под работу с SystemVerilog заточены современные САПРы (системы автоматизированного проектирования) для моделирования и логического синтеза цифровых схем. Также популярны языки VHDL и Verilog. Под синтезом цифровых схем подразумевается процесс превращения функционального RTL-кода в логическую схему (netlist) — набор соединённых сигнальными цепями простых логических элементов (И, НЕ, И-НЕ, ИЛИ, защелки, триггеры и др.).

Далее в процессе синтеза эти логические элементы заменяются на эквивалентные физические — так называемые стандартные ячейки, поставляемые фабрикой под конкретный технологический процесс. Кстати, примерно в одно время с фронтенд-инженерами начинают свою работу команды прототипирования (FPGA) и софта, ведь микросхема без программного обеспечения — просто кирпич.

Результат работы фронтенд-команды передается нам, команде физического дизайна (в народе — топологам). Этот результат может быть представлен в виде готового netlist или RTL-описания — в последнем случае мы делаем логический синтез сами.

С помощью специальных САПР и технологических данных от фабрики мы проводим физический синтез цифровой схемы, то есть проектируем ее топологию. Планируем размеры чипа, размещаем стандартные ячейки, блоки компактной памяти (например SRAM), аналоговые схемы и сопутствующие физические структуры на площади чипа. Выполняем трассировку питания и сигналов внутри чипа. Результат нашей работы — набор слоев с транзисторами и межсоединениями в виде GDS-файла (GDS, Graphic Database System, графическая база данных). Этот файл мы передаем на фабрику.

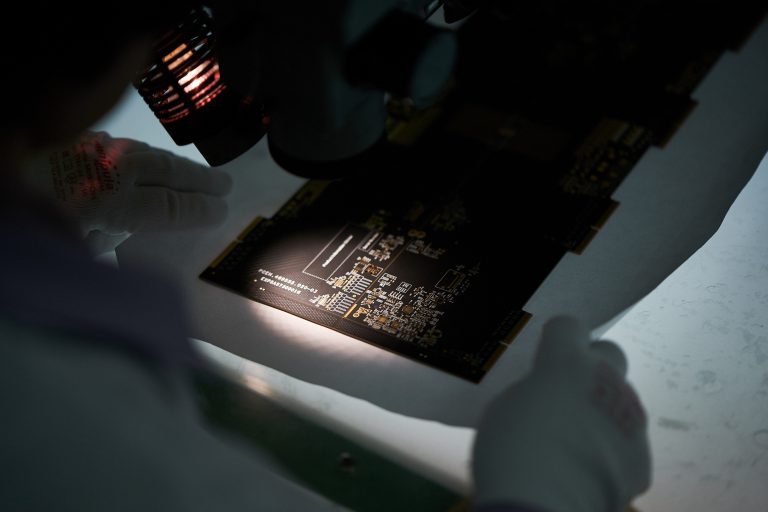

На основе GDS-файла на фабрике изготавливают фотошаблоны для производства микросхем. После производства чипы отделяются от кремниевой пластины, корпусируются и занимают свое место в готовых устройствах: серверах, чипсетах, телефонах и роботах.

Сегодня системы на кристалле сочетают много разных блоков в дополнение к CPU, так что работа выходит масштабная. Миниатюризация идет не только в кремнии, но и вокруг него. Оперативную память ставят максимально близко к кристаллу СнК (SoC). Корпуса делают компактными, оперативную память — многослойной, печатные платы — модульными.

На основе чипов формируют процессорные микросборки. Основной модуль с чипсетом, СнК и необходимой рассыпухой (конденсаторы, резисторы, стабилизаторы напряжения и пр.) унифицируется. По форме готового продукта создается отдельная плата с портами и интерфейсами. Так можно снизить цену монтажа, изготовления, и расширить возможности интеграции продуктов.

Взаимодействие между командами

Системы на чипе, как я уже говорил, состоят из множества блоков. Например, в современных SoC для смартфонов блоки GPU и CPU (графического и центрального процессоров) занимают не более четверти и трети всего чипа соответственно. Остальное — это интерфейсы, блоки DSP (DSP, digital signal processing — цифровая обработка сигнала), ядра искусственного интеллекта и другие компоненты, например модемы 4G/5G.

Усложнение архитектуры микросхем ведет к тому, что весь объем работы, например, на этапе физического синтеза, уже невозможно выполнить в одиночку, как это было раньше, когда один бэкенд-инженер мог пройти путь от RTL до GDS для всего чипа сам. Сейчас необходимо диверсифицировать процесс проектирования и работать в команде.

У нас, топологов, командная работа организована так же, как и в других командах в IT-индустрии, будь то FPGA-команда или фронтенд-команда. Мы как бэкенд-инженеры напрямую взаимодействуем с фронтенд-командой (фронтенд-инженерами), принимаем от них RTL-описания и используем их в дальнейшем. Новичкам-фронтендерам поручают создание RTL для блоков поменьше, а процессорными ядрами или сложными интерфейсами вроде DDR и PCIe могут вообще заниматься другие компании — и с ними взаимодействуют только как с поставщиками готовых решений. Так, Qualcomm покупает ядра ARM для своих SoC.

Кроме фронтендов, мы взаимодействуем с командой DFT (Design for Test), которая занимается интеграцией тестовых структур. Это очень важно на этапе проверки чипа после производства (post-silicon verification), когда с помощью тестов нужно убедиться, что все блоки в чипе работают правильно и на нужной частоте. Команда DFT работает с проектом на этапе и написания RTL, и физического синтеза. Соответственно, DFT-инженеры взаимодействуют и с RTL-командой, и с нами.

Важно отметить, что над проектом трудятся одновременно и другие команды, например команда функциональной верификации, но, поскольку мы не взаимодействуем с ними напрямую, я не отметил их на схеме.

В YADRO топологи также напрямую взаимодействуют с package team — командой разработки корпуса для чипа. В основном мы отправляем им данные о задержках внутри кремния до площадок ввода/вывода на чипе, а также расположение самих площадок. Это нужно им, чтобы грамотно спроектировать корпус для будущей микросхемы.

Физическое проектирование SoC в YADRO

Как только мы получили данные от фронтендов, можно приступать к проектированию топологии: я выделил три основных шага в маршруте физического синтеза.

Первый шаг начинается с подготовки в САПР площади, «коробки», для размещения логики или подсистемы СнК — это так называемая зона ядра (core area). В ее границах расставляют большие макроблоки (PLL, аналоговые части больших интерфейсов вроде PCIe

Другой важный этап — это подготовка сетки питания для питания всех транзисторов в схеме. Сетка также ограничивает плотность трассировки сигналов, так как делит с ними одни и те же слои. Топология микросхемы собирается как слоеный пирог: самый нижний слой занимают транзисторы, а выше идут слои металлов, в которых «вытравливаются» дорожки — будущие сигнальные межсоединения.

После подготовки core area и сетки питания, когда разместили контактные площадки, бампы, порты памяти и прочее, мы приступаем к автоматизированным этапам. Первый — размещение стандартной логики и ее оптимизация. Мы получаем логику как результат логического синтеза RTL и размещаем на реальной площади.

После размещения логики нужно провести трассировку ее межсоединений. В зависимости от инструментария это можно делать в той же самой САПР или в другом софте. Здесь виртуальные цепи становятся физическими. Чтобы при трассировке сигналов не пострадали их задержки, нужно просчитать их длину, влияние друг на друга, оптимизировать число переходов между слоями, при необходимости переставить некоторые стандартные ячейки ближе друг к другу.

Каждый шаг в физическом синтезе сопровождается своими проверками, а после трассировки приходит черед финальных проверок. Мы называем это signoff-стадией. Здесь мы проводим финальный статический временной анализ (STA, Static Timing Analysis) задержек сигналов в микросхеме. Рассчитываем SI (signal integrity, влияние сигналов друг на друга), влияние экстракции паразитных параметров схемы (RC Extraction) и металлической заливки пустых областей (Metal Fill), оцениваем потребляемую мощности микросхемы (PI, Power Integrity).

В signoff также входят физические проверки: фабрика ждет от нас отчетов по DRC (Design Rule Check), проверки соблюдения геометрических норм, необходимых для производства. Помимо DRC мы проводим электрическую проверку (LVS, Layout vs Schematic): перед signoff мы сравниваем схему, полученную обратным методом из нашего GDS-файла, с исходной электрической схемой, полученной после физического синтеза.

PPA — Performance Power Area

PPA — это баланс трех характеристик, каждую из которых мы стремимся улучшить в процессе логического и физического синтеза:

Микросхемы разного назначения могут быть сбалансированы по-разному. Серверные решения — в сторону производительности, а мобильные — в сторону снижения потребления. Можно было бы заниматься оптимизацией сколько угодно, но у нас есть ограничивающий фактор — time-to-market. К определенному моменту мы должны прийти к консенсусу, чтобы вовремя выпустить чип.

Метрика качества QoR (quality of results)

Метрику качества мы рассчитываем на каждом этапе. Например, еще при планировании площадки можно передвинуть память, чтобы логика могла быстрее к ней обращаться. Также мы можем улучшать временны́е характеристики в отрыве от оптимизации размещения. Менять стандартную логику, предоставляемую фабрикой, делать ее чуть быстрее и энергоэффективнее или наоборот. Таким же образом можно оптимизировать дерево синхросигналов, чтобы снизить его задержку и ускорить доставку тактового сигнала до потребителей (триггеров, SRAM).

Чтобы уменьшить потребляемую мощность схемы и нагрузку на сетку питания чипа, используем более медленные ячейки с более низким энергопотреблением, где это возможно. Если для получения нужных PPA-характеристик чипа этого недостаточно, то можно подать результаты физического синтеза в виде обратной связи и провести повторный логический синтез исходного RTL. САПР будет использовать эту информацию при декомпозиции RTL-функций и оптимизации стандартной логики. Как видите, возможностей что-то поправить в проекте здесь много.

Технология, библиотеки, нанометры

Технология в нашем контексте — это процесс, заточенный под определенную структуру, под разрешающую способность литографа. Разрешающая способность обычного литографа — 193 нм, это ультрафиолет (UV). Длина волны UV-лазера позволяет нам получать структуры с точностью до 7 нм, но на практике с обычным UV это очень сложно. Поэтому на таком литографическом оборудовании индустрия ограничивается 14−16 нм. Чтобы с длиной волны в 193 нм получить 14-нанометровый транзистор, фабрики используют мультифотошаблоны, иммерсивную литографию и другие хитрые приемы.

Сейчас в тонких техпроцессах распространение получил экстремальный ультрафиолет (EUV) с длиной волны 13,5 нм. Он позволяет получать структуры до 3 нм, и это еще не предел. У столь малой длины волны есть свои недостатки: ее излучение не фокусируется обычными оптическими линзами, и для решения этой задачи используют точные зеркала со специальным покрытием.

Библиотеки, которыми мы пользуемся, обычно состоят из двух основных компонентов — PDK и DDK. PDK содержит технологические данные и данные для аналогового дизайна. DDK — это цифровые библиотеки, включающие стандартный набор логики, что мы используем для синтеза цифровой части СнК. В него также могут быть включены компиляторы статической памяти. Все это сопровождается документацией.

Как я уже говорил, топология микросхемы собирается как слоеный пирог: в самом нижнем слое транзисторы, а выше — слои металлов. Последних может насчитываться пять, а может и больше десяти — зависит от того, что предлагает фабрика. Это влияет на цену изготовления чипов и возможность реализации проектов определенной сложности. Все металлические слои обычно делают из меди, а самый верхний — из алюминия. На этом слое формируют контакты для подключения к чипу снаружи, в корпусе.

Цифровой vs аналоговый бэкенд

В цифровом дизайне, в отличие от аналогового, мы не работаем с отдельными транзисторами, вместо них у нас стандартные ячейки. Они представляют собой элементы, выполняющие определенную логическую функцию (AND, OR, XOR) или триггер. SPICE-моделирование схемы мы тоже не проводим. Для расчета временны́х характеристик используем liberty-формат — это упрощенные статистические модели задержек, где данные представлены в виде таблиц, а не функций. В зависимости от условий САПР получает нужные задержки методом интерполяции.

В отличие от аналоговой разработки, цифровой дизайн имеет строгие ограничения на размещение логических элементов. Они вызваны тем, что в зависимости от сложности блока или СнК в целом количество ячеек, размещаемых и трассируемых одновременно, может достигать десятков миллионов. Чтобы САПРы могли обрабатывать такое число стандартных ячеек, их нужно организовывать в ряды, одинаковые или кратные по высоте. Ширина и размещение контактов у стандартных ячеек также жестко квантуется.

На картинке слева — массив стандартных ячеек. Они четко вписаны в ряды. Далее — ячейка двухвходового элемента AND в САПР и GDS-файле, который идет на фабрику. Справа — снимок с электронного микроскопа после травления микросхемы. Можно увидеть много мусора от травления, решетку FinFET и прийти к выводу, что она получилась весьма неровной. Да, если мы нарисуем ровные прямоугольники, в итоге будут изготовлены немного неровные. К счастью, это заранее рассчитывается, оптические эффекты компенсируются, и в 98% случаев мы получаем транзисторы с нужными характеристиками.

Результат нашей работы

Как уже писал выше, мы производим финальные signoff-проверки: STA, PI, PV и другие. Далее мы заполняем технологические формы для фабрики, готовим GDS-файл с его md5-хешем, отчет о геометрической верификации (DRC report) и отправляем все на фабрику.

Пока чип «пекут» на фабрике, мы делаем другой проект. После того как к нам возвращается готовый чип, за него берутся команды bring-up и post-silicon verification. Они запускают кристалл на тестовой плате и проверяют его. Если находят какой-нибудь баг, мы также перепроверяем результаты своей работы в физической модели.

Разработка микросхемы — это сложный процесс со стороны фронтенда и бэкенда, верификации и интеграции, вообще вне зависимости от этапа RnD. Разработка требует множества компетенций, узкой специализации, которую получают в университете и затем развивают годами. Физическое проектирование, которым занимается моя команда, — один из ключевых этапов разработки.

У нас интересные, захватывающие задачи и много красивых картинок, хотя 80% времени все равно приходится смотреть на логи и код.

Что почитать по дизайну микросхем

Чтобы глубже погрузиться в разработку микросхем, рекомендую читать блоги инженерных компаний на Хабре и других ресурсах, а также «Истовый инженер». Если больше интересна VLSI-тематика, топология, то самым полезным ресурсом будет deepchip.com. Также стоит обратить внимание на wikichip.org. vlsi-expert.com, vlsiguru.com.

Из книг рекомендую, конечно, «Цифровую схемотехнику и архитектура компьютера» Харрисов (второе издание от Imagination), а также Static Timing Analysis for Nanometer Designs под авторством Д. Башкера и Р. Чадхи.

Вместо тысячи слов: SoC Design Challenge

Сложно рассказать обо всех процессах простыми словами — лучше один раз увидеть. Для этого рекомендую поучаствовать в хакатоне, который мы каждый год проводим в МИЭТ в Зеленограде. На хакатоне представлено четыре основных трека: топологическое проектирование, UVM-верификация, системная верификация СнК и RTL-проектирование. Ждем ваших заявок до 18 марта!

Здравствуйте! в каких САПР вы работаете? проводите ли вы стажировки?

Добрый день! Мы работаем в современных САПР, но, к сожалению, более подробно рассказать не можем — закрытая информация. Стажировки проводим, подробности вы найдете по этой ссылке.