Как стать топологом интегральных схем: от первой лабораторной с D-триггером к реальной инженерной практике

Профессия тополога — одна из самых закрытых, недооцененных и в то же время важных в современной микроэлектронике. Именно топологи цифровых интегральных микросхем (ИМС) расставляют миллиарды транзисторов на кристалле кремния и заставляют их работать как единое целое, превращая схему в процессор. Они участвуют в создании всей современной электроники — от мобильных устройств до космической аппаратуры, процессорных ядер и систем связи 5G.

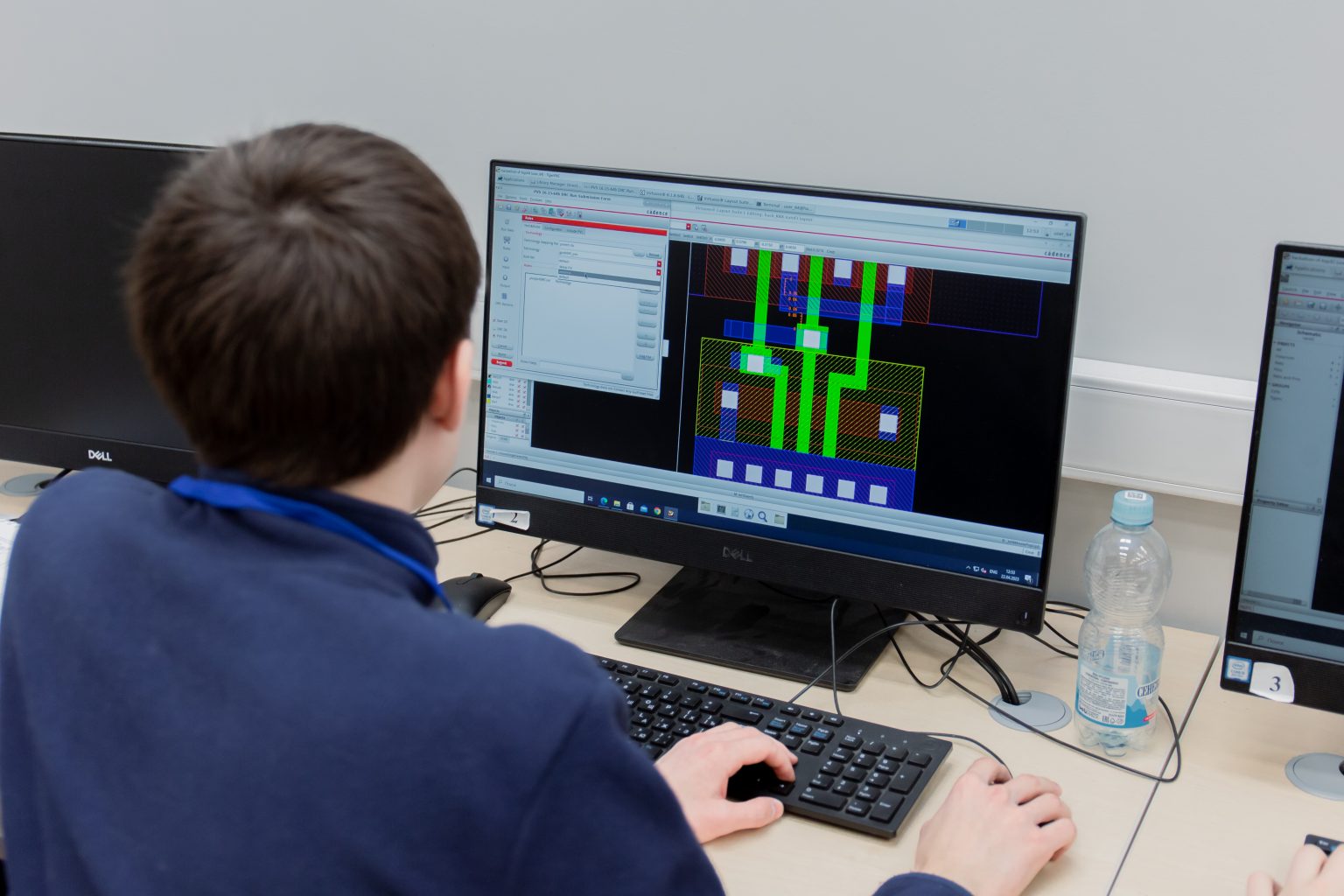

Илья Пеплов, старший инженер по разработке СнК в отделе физического синтеза полупроводников YADRO, подробно рассказывает о своей профессии: чем физический дизайнер отличается от других топологов, где этому учат и почему спрос на таких специалистов очень высокий.

- где заканчивается код и начинается кремний

- почему тополог и архитектор смотрят на один и тот же чип по-разному

- как понять, что это ваша область и какие знания нужны топологу интегральных схем

- список университетов, которые выпускают топологов

Кто такой тополог

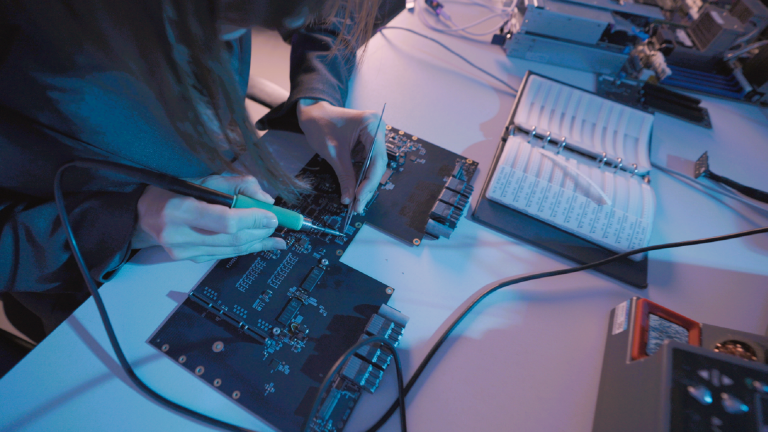

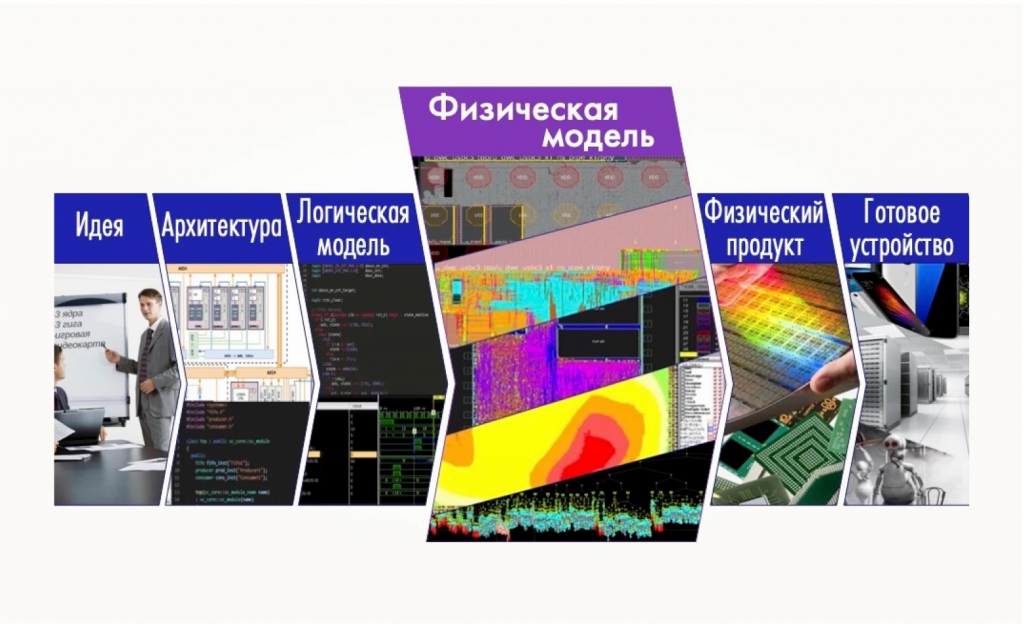

Если обобщить, то тополог — это инженер, который на основании электрической схемы разрабатывает ее физическое представление. Он размещает элементы схемы на подложке и соединяет их между собой проводниками по правилам технологии и электротехники.

Существует несколько направлений в разработке топологии в микроэлектронике. Рассказываю в порядке уменьшения масштаба, от миллиметров к нанометрам:

- Печатные платы (PCB design), масштаб: сотни мм → сотни мкм.

- Корпуса микросхем (IC Package design), масштаб: десятки мм → единицы мкм.

- Интегральные микросхемы (IC design), масштаб: единицы мм → единицы нм.

Физический синтез цифровых ИМС — моя область компетенций. Далее в тексте упоминая тополога я буду иметь в виду область физического дизайна. Понять масштаб работы и зону ответственности поможет моя прошлая статья о проектировании топологии при разработке микросхем.

Кто такой физический дизайнер

В последнее входит расположение транзисторов, проводников, цепей питания, сигналов и многое другое.

Роль физического дизайнера в цепочке разработки микросхем

Может показаться, что мы включаемся в работу, только когда архитектура продумана, RTL-код написан, а логика проверена. Но, если ждать этого момента, проект почти гарантированно выйдет за сроки.

На этапе проектирования архитектуры физдизайнер выступает как эксперт-консультант. Он помогает архитекторам оценивать конструкцию чипа с физической точки зрения:

- Какая максимальная площадь возможна под определенную технологию?

- Будут ли узкие места при трассировке?

- Какие блоки лучше расположить ближе друг к другу?

- Где стоит заранее учитывать конфликты интерфейсов?

Архитектор мыслит крупными категориями (подсистемами) — ядрами, шинами, контроллерами. Тополог мыслит площадями и физическими связями, может представить объем отдельных подсистем и то, как их лучше организовать на площади будущего чипа.

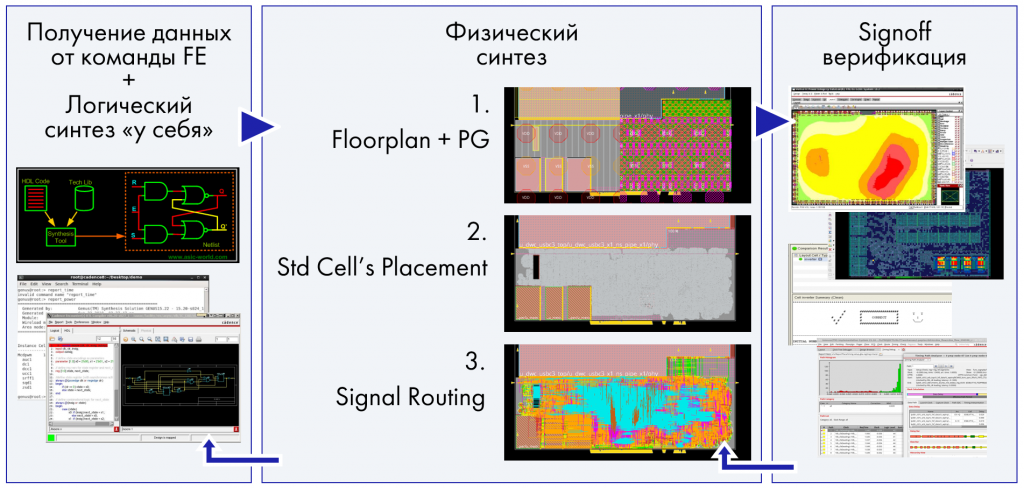

Когда RTL-код проекта или его отдельных подсистем достаточно стабилен, чтобы его синтезировать и имплементировать, мы беремся за работу. Синтезируем RTL-код, размещаем элементы, блоки памяти и устройства на площади кристалла, настраиваем алгоритмы размещения стандартных ячеек и трассировки, а также проводим проверки, например: временны́х характеристик (STA), электрической целостности (LVS, Layout vs Schematic), потребляемой мощности (PI, Power Integrity), геометрической целостности (DRC, Design Rule Check) и другие.

Если после анализа становится ясно, что блок не укладывается в заданные характеристики — например, не достигается целевая частота, мы пробуем исправить проблему локально. Для этого применяются ручные правки, такие как изменение размещения элементов или параметров трассировки. Если локальные меры не дают результата, формируется обратная связь для архитектора и RTL-дизайнера в команду фронтенда.

Как инженеры выбирают маршрут проектирования топологии

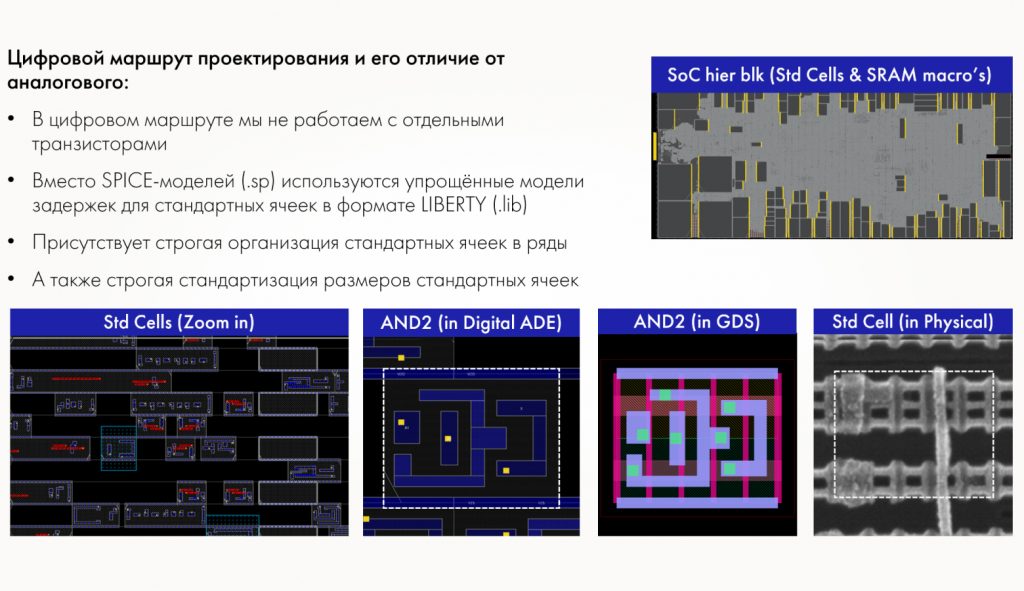

Маршрут разработки топологии ИМС можно разделить на два основных типа — цифровой и аналоговый. При этом не стоит объединять эти понятия с самими цифровыми и аналоговыми интегральными схемами. Например, топологию цифровой ИМС может разрабатываться по аналоговому маршруту, а топология аналоговой ИМС по цифровому.

Аналоговый маршрут проектирования

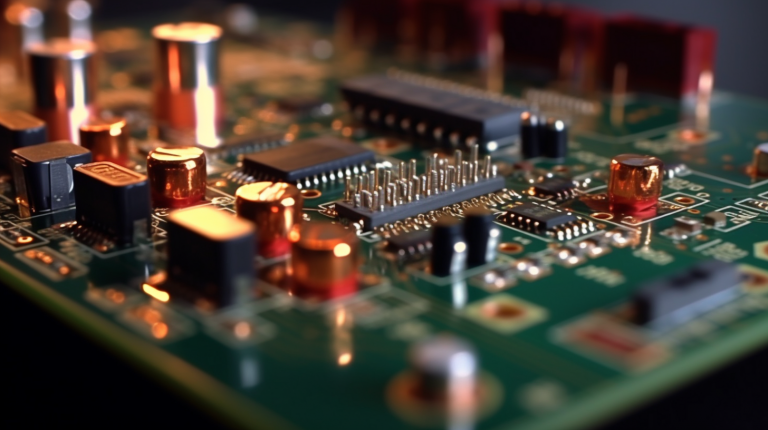

Аналоговый маршрут проектирования ИМС позволяет создавать электрические схемы и физические структуры на уровне отдельных транзисторов и пассивных элементов — резисторов, конденсаторов и других. При таком подходе инженер может управлять каждым параметром схемы.

Помимо абсолютной схемотехнической гибкости, которую ограничивает лишь сама технология производства, этот маршрут имеет один большой недостаток. Аналоговое функциональное моделирование (например, SPICE) рассчитывает поведение каждого элемента схемы — транзистора, резистора или емкости непрерывно, на основании непростых дифференциальных уравнений, использующих не одну сотню технологических параметров. Это требует огромных вычислительных мощностей. В результате количество активных элементов, прежде всего транзисторов в ИМС, разработанных аналоговым маршрутом, редко превышает тысяч штук.

Цифровой маршрут проектирования

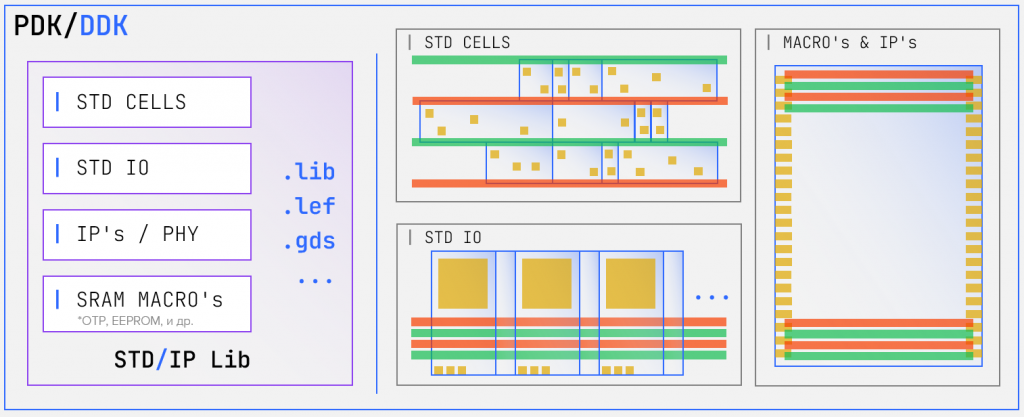

Цифровой маршрут проектирования ИМС работает с готовыми элементами — транзисторными сборками, но сами отдельные транзисторы остаются за кадром. Эти сборки представляют собой «черные ящики» с входами и выходами, местами подключения сигналов и питания, и даже с готовой топологией. На их основе получаются логические элементы (элементы двоичной логики) и сложно-функциональные макроблоки, которые уже формируют библиотеки для цифрового проектирования ИМС.

Например, для логических элементов это библиотеки стандартных ячеек, таких как известные по двоичной логике И, ИЛИ, НЕ и более сложные. Для расчета характеристик элементов цифровых библиотек и интегральных схем из них используются статистические модели задержек, а сам процесс называется статическим временным анализом (STA, Static Timing Analysis).

Проще говоря, статистические модели задержек — это набор упрощенных результатов аналогового моделирования каждого логического элемента или макроблока из библиотеки. Эти результаты заранее рассчитаны для строго определенного набора технологических параметров и внешних условий.

Поскольку в цифровой логике для нас интересны только два логических уровня — 0 и 1, такой подход сильно ускоряет анализ задержек и функционального моделирования цифровых схем. В итоге он позволяет проектировать схемы из десятков миллионов логических элементов (миллиардов транзисторов). Более подробно про маршруты описано в статье.

Тополог: редкая профессия с постоянным спросом

Дефицит цифровых и аналоговых топологов огромный, и ситуация не меняется уже много лет. А в последние годы спрос стал еще выше. Физдизайнеров обычно ищут компании, которые занимаются:

- разработкой процессоров, контроллеров, SoC,

- разработкой коммуникационных IP-блоков,

- созданием промышленных или узко-специализированных микросхем,

- заказным проектированием для других компаний.

Особенно нужны цифровые топологи: количество задач не соответствует числу специалистов на рынке. На втором месте аналоговые топологи. Это узкая, очень сложная область, и хорошие специалисты — редкость. Если вы уже начинающий или опытный тополог и ищете сферу применения своих навыков, присмотритесь к вакансиям в YADRO. Вы можете воспользоваться поиском и отфильтровать их по нужному запросу, например СнК.

Какими навыками должен обладать тополог

Топология — это профессия на стыке инженерии, логики, усидчивости, творчества и большого терпения. Недостаточно просто знать электротехнику или уметь работать с промышленными системами автоматизированного проектирования (САПР). Хорошего тополога отличает не набор программ, а набор привычек и характера.

Усидчивость — фундамент ежедневной работы

Большая часть топологии — это долгая работа над одним блоком, необходимость много раз пересматривать одни и те же места, внимательность к мелким деталям и бытовая «неустрашимость» перед рутиной.

Многие задачи требуют 10, 20 и даже 50 итераций, постоянного изменения параметров и поиска причин неожиданных ошибок. Если инженер быстро устает от повторения или не любит копаться в мелочах, ему будет тяжело.

Терпение и умение работать с неопределенностью

Топология редко идет линейно. Часто САПР не может проложить трассу, временные характеристики «не сходятся» или правки RTL приходят в последний момент. Или нужно решить сложную инженерную задачу, найти компромиссное решение

Способность находить обходные пути

Тополог не должен сдаваться при первой же проблеме. Когда автоматизация не справляется:

- он подбирает параметры,

- экспериментирует с алгоритмами,

- пробует ручные исправления,

- пишет собственные скрипты и консольные команды,

- ищет новые маршруты решения.

Тут играет роль инженерная изобретательность.

Аккуратность и внимательность

Одна ошибка — и ты ошибся. Весь проект может перестать работать, поэтому физдизайнеру нужно:

- следить за чистотой входных данных, внимательно смотреть логи,

- анализировать тайминги и уметь их отлаживать, внимательно смотреть логи,

- проверять и анализировать цепи питания, сигналов и синхросигналов,

- уметь и хотеть искать первопричину любой подозрительной ситуации.

Умение работать с большим объемом данных

Чипы становятся все больше: десятки различных подсистем, миллиарды транзисторов, миллионы сигналов, десятки уровней металлизации.

Где учиться, чтобы стать физическим дизайнером

Стать инженером-топологом цифровых ИМС без высшего образования практически невозможно: эта профессия требует фундаментальных знаний в электронике, физике полупроводников, схемотехнике и работе в САПР. Поэтому путь почти всегда начинается в университете. Но важен не только выбор вуза, но и программы обучения, где дают правильную базу и есть доступ к профессиональным инструментам.

Московский институт электронной техники (МИЭТ)

Это основной вуз, где профессиональная подготовка топологов поставлена системно. МИЭТ исторически специализируется на микроэлектронике, имеет базовые кафедры и тесные связи с индустрией, обеспечивает студентов доступом к САПР.

Я учился в МИЭТ по специальности

- 11.03.01

и 11.04.01 — «Радиотехника», - 11.05.01 — «Радиоэлектронные системы и комплексы»,

- 12.03.01

и 12.04.01 — «Приборостроение».

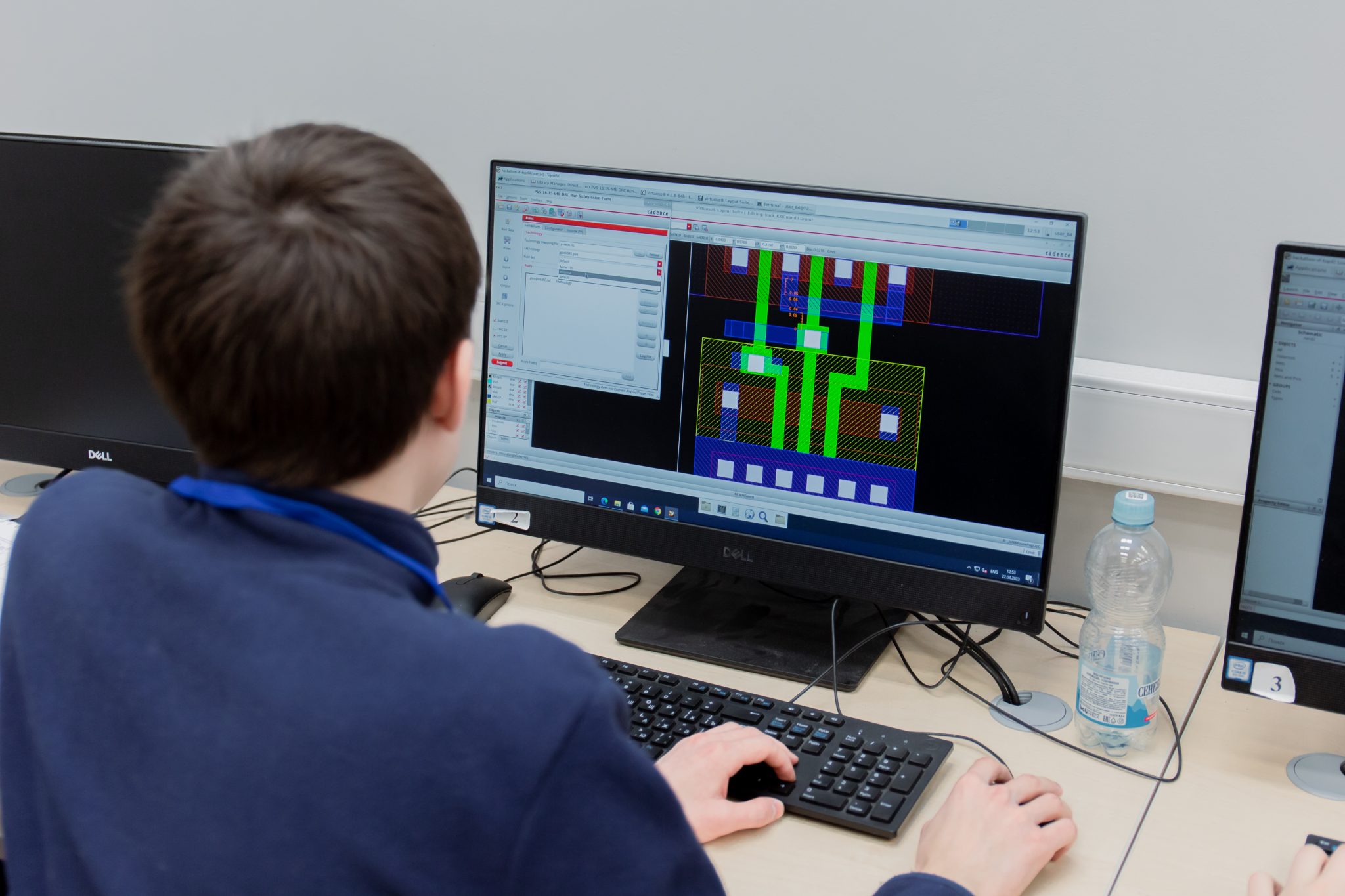

Помню момент, который окончательно определил мое будущее. На лабораторной нам нужно было развести D-триггер — небольшой логический элемент примерно из 18 транзисторов. Большинство ребят делали топологию в обычном многоуровневом варианте, как и требовалось по заданию. А я решил попробовать уложить все в один слой металлизации. Это не только не требовалось — по-хорошему, так даже делать не стоило. Но мне было интересно проверить, смогу ли я разместить все транзисторы и соединения так, чтобы они не пересекались и при этом схема оставалась рабочей.

Чтобы узнать о старте следующего потока первыми, подпишитесь на рассылку.

МИФИ (Национальный исследовательский ядерный университет)

МИФИ также дает хорошую фундаментальную физическую и техническую базу. Здесь преподают схемотехнику, электронику и дисциплины по проектированию микросхем. Эту подготовку дают, например бакалавриат

МГУ (Московский государственный университет)

В МГУ есть кафедры и лаборатории, связанные с проектированием интегральных схем. Сильные стороны: глубокая физическая база, научная подготовка и лаборатории, работающие с топологией и дизайном чипов.

Университеты готовят недостаточно много специалистов. И даже внутри одного вуза одни кафедры дают хорошую подготовку по физдизайну, другие почти не касаются разработки интегральных схем и больше сфокусированы на подготовке специалистов по разработке ПО, или, например, готовят инженеров-технологов для работы на полупроводниковых фабриках.

В профессию физдизайнера — высокий порог входа. Помимо сложности работы, есть две объективные преграды:

- Профессиональные САПР проприетарные и дорогие. Их нельзя просто скачать, только купить за десятки тысяч долларов.

- Технологии производства микросхем закрыты. Библиотеки стандартных ячеек, PDK (process design kit) и технологические файлы — коммерческая тайна фабрик.

Университеты дают доступ и к инструментам, и к учебным технологиям, что делает обучение реальным. Более подробно про магистерскую программу МИЭТ и YADRO писали в статье.

Знания, без которых будет сложно

Профессия тополога находится на пересечении физики, электроники, информатики и инженерной логики. Поэтому нельзя выделить один единственный курс, после которого студент становится готовым специалистом. Топология требует широкой базы, и она формируется через несколько ключевых дисциплин.

Электротехника — фундамент для будущего инженера-тополога

Здесь студенты изучают понятия тока, напряжения, сопротивления, основы электромагнетизма. Узнают, что такое емкость и индуктивность, как ведут себя элементы цепи и куда «пойдет» ток в сложной структуре.

Для физдизайнера эти знания критически важны: чтобы понять, почему возникают задержки, просадки питания, нужно чувствовать электрическую цепь. Даже цифровая логика, построенная на нулях и единицах, в реальности состоит из транзисторов и проводников, подчиняющихся законам электротехники.

Цифровая схемотехника — язык цифровой электроники

Если электротехника дает физическую интуицию, то цифровая схемотехника формирует логическое мышление инженера. Здесь студент знакомится с логическими элементами (И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ), с триггерами, регистрами, счетчиками, с путями данных и устройством цифровых блоков, а также с процессорной логикой.

Большая часть цифровой топологии — это размещение стандартных ячеек. Чтобы понимать ограничение по времени распространения сигнала, нужно знать, как работают триггеры и пути данных.

По сути, цифровая схемотехника объясняет, что именно вы раскладываете на кремнии и почему одни блоки сложнее других.

Спецкурсы по проектированию интегральных схем — первый шаг к реальным САПР

Эти дисциплины обычно появляются в магистратуре или на старших курсах бакалавриата. Они включают:

- основы RTL-разработки (Verilog, SystemVerilog, VHDL),

- технология производства ИМС,

- логический синтез цифровых схем,

- знакомство с промышленными САПР,

- физический синтез: выполнение лабораторных по размещению и трассировке,

- оптимизацию цифровых блоков по производительности, потреблению и площади (PPA, Performance Power Area),

- моделирование работы схем, пост-топологические исследования.

Как освоить топологию самостоятельно

В IT многие направления давно перешли в режим «выучи дома → сделай pet-проект → получи работу». Но с топологией все иначе.

Есть теоретическая база, которую можно освоить даже дома: электротехника на уровне базовых законов, цифровая схемотехника, основы архитектуры компьютеров и фундамент цифровых логических схем. Ниже — список источников.

- Хоровиц и Хилл — «Искусство схемотехники». Отличная база по электронике, много практики и интуитивных объяснений.

- Харрис и Харрис — «Цифровая схемотехника». Одна из лучших книг для будущих топологов: логика, архитектура, CMOS. Есть русский перевод.

Книги по КМОП-логике:

- Weste & Harris — «CMOS VLSI Design»,

- Rabaey — «Digital Integrated Circuits»,

- Shen & Schaumont — «Logic Synthesis and Verification».

Самая большая трудность в том, что физический синтез невозможен без профессиональных САПР — это десятки специализированных программ. Наиболее известные из них:

- Cadence Innovus,

- Synopsys ICC2,

- Mentor Graphics Calibre.

Лицензии стоят очень дорого, безумно дорого. Доступ к техническим процессам тоже закрыт: фабрики не публикуют PDK.

Тем не менее, есть некоторые открытые САПР. Например, OpenROAD, Magic, Qflow и OpenLane. Их синтаксис и маршруты сильно отличаются от промышленных САПР, но при желании на них можно потренироваться и получить хоть какую-то практику.

Университетские программы остаются основным путем — туда поставляют лицензии САПР, там работают преподаватели, которые знают workflow промышленности, есть проектные команды и реальные задачи, нередко поставляемые индустриальным партнером программы.

Первые практические шаги в топологию: открыть САПР и начать

Если вы только начинаете интересоваться топологией, самое главное — пробовать. Один раз открыть САПР — например, open source-маршрут проектирования Open Lane 2 и попробовать учебный проект. Написать строчку собственного RTL-кода, синтезировать его в стандартную логику и пройти этапы размещения и трассировки.

Можно попробовать свои силы на хакатоне SoC Design Challenge. Это одно из самых доступных мест, где можно впервые прикоснуться к современным САПРам и реальному маршруту разработки чипов. Далее рекомендую пройти курс по схемотехнике. Он не про цифровую топологию напрямую, но дает фундамент — понимание транзисторов, логики, задержек, питания и реальных электрических ограничений.

Не бойтесь того, что вход в профессию выглядит трудным. Да, порог высокий, доступ к инструментам ограничен, но это ощущение проходит, когда появляется первый результат — маленькая топология, первый работающий блок, успешная защита проекта.

Когда я оглядываюсь назад, мне кажется, что путь в топологию был совершенно случайным, но одновременно очень закономерным. Случайным, потому что я долго не понимал, чем хочу заниматься, и буквально «провалился» в эту область через одну лабораторную работу. Закономерным, потому что именно в топологии сошлось все, что мне нравится: задачи на логику, ощущение реального инженерного ремесла и возможность видеть результат своей работы в самых буквальных формах — в кремнии.