Список литературы для тех, кто хочет разобраться в специализированных процессорах

с помощью нейросети

Спецпроцессоры не настолько известны, как универсальные процессоры. Действительно, куда им до популярности той же архитектуры RISC-V! Которая, впрочем, спроектирована в том числе для использования множества специализированных ускорителей. Современный универсальный процессор все чаще выполняет роль «дирижера», основное занятие которого — управление «оркестром» разнообразных спецпроцессоров. В статье собрали список материалов, которые помогут глубже понять принципы работы, проектирования и программирования таких процессоров.

Подборку составил и прокомментировал Пётр Советов, специалист в области разработки DSL-компиляторов и старший научный сотрудник лаборатории специализированных вычислительных систем РТУ МИРЭА. Книги и статьи на русском и английском языках будут полезны как начинающим, так и практикам, стремящимся углубить свои знания в области специализированных процессоров.

- почему спецпроцессоры важны для энергоэффективности и решения специфических задач

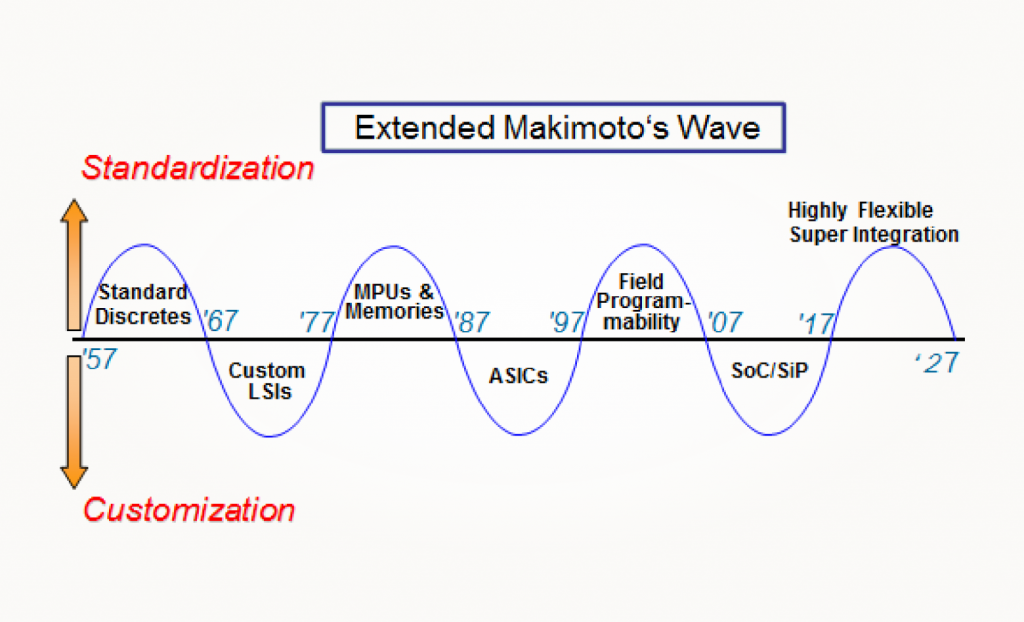

- как волна Макимото описывает циклы специализации и стандартизации в микроэлектронике

- примеры развития архитектур от FPU до TPU и от GPGPU к тензорным ускорителям

- какова роль компиляторов и языков описания архитектур (ADL) в создании спецпроцессоров

Ключ к энергоэффективности и разнообразию архитектур

Специализированные архитектуры сегодня переживают расцвет, и этот факт отражен в известной тьюринговской лекции «Новый золотой век компьютерной архитектуры» Дэвида Паттерсона и Джона Хеннесси. У спецпроцессоров есть самые разные воплощения: специализированные расширения команд, спецблоки на уровне ядра, предметно-ориентированные ускорители в составе системы на кристалле или внешние решения на PCIe-карте.

Например, на чипе Apple A12 исследователи насчитали 42 различных аппаратных ускорителя. Их архитектура не содержит ничего «лишнего» и нацелена на узкий класс решаемых задач, зачастую с использованием разнообразных форм параллелизма. Таким образом, достигаются более высокие показатели энергоэффективности, чем у универсальных ядер. Спецпроцессоры проектируются для различных задач машинного обучения, криптографии, обработки изображений, видео, звука, сетевых пакетов, сенсорной информации и так далее.

С точки зрения аппаратного проектирования спецпроцессоры заслуживают особого внимания, поскольку специализация приводит к целому зоопарку нестандартных архитектурных решений. Многие из них казались давно забытыми или представляли чисто академический интерес.

Спецпроцессоры важно проектировать быстро, поэтому именно для них была придумана передовая методика совместного программно-аппаратного проектирования (SW/HW Codesign). Кроме того, спецпроцессоры интересны разработчикам компиляторов: современные спецархитектуры часто программируются на разнообразных специальных языках (DSL), а при компиляции необходимо использовать весьма нетривиальные методы.

Ниже — краткий, начальный обзор литературы по спецпроцессорам. Если тема вам интересна, пишите в комментариях — мы выпустим продолжение статьи.

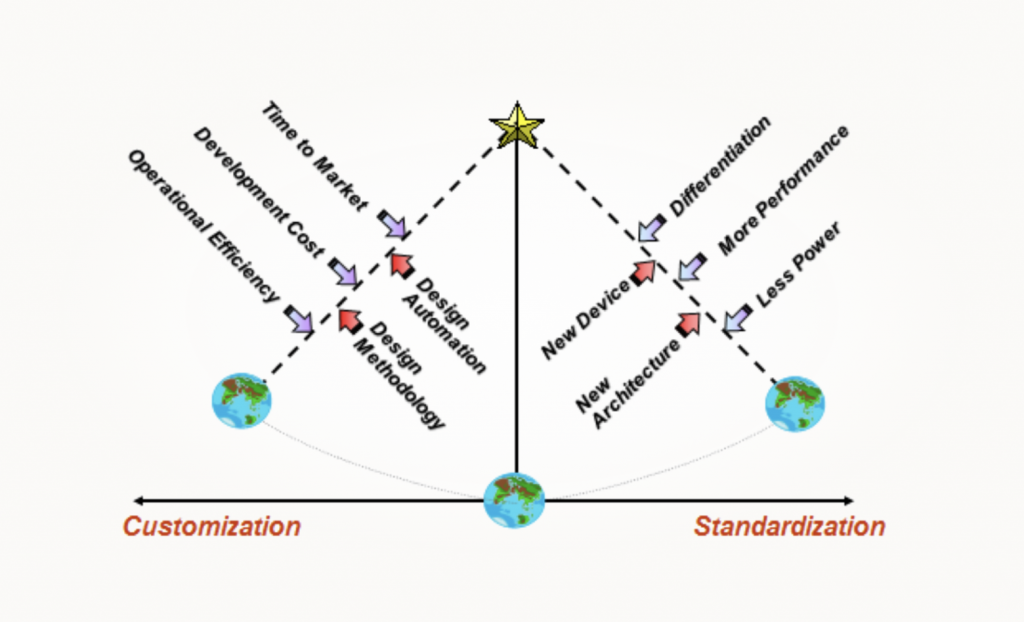

«Implications of Makimoto’s Wave», Tsugio Makimoto

Хорошо известны эмпирические законы Мура и Деннарда:

- Мур предположил, что количество транзисторов, размещаемых на микросхеме, удваивается примерно каждые 18−24 месяца, при этом стоимость производства транзистора уменьшается.

- Деннард сформулировал принцип масштабируемости транзисторов: при уменьшении размеров транзистора его производительность сохраняется, энергопотребление на единицу площади уменьшается, а плотность размещения увеличивается.

Волна Макимото — это еще один эмпирический закон, который гласит, что тенденции в микроэлектронике периодически меняются от универсальных (стандартных) решений к специализированным и обратно.

Несколько примеров работы такого «маятника»:

- В 1980-х годах математический сопроцессор представлял собой отдельную микросхему. Прошло время, и FPU стал лишь одним из многих блоков исполнения процессора общего назначения.

- Затем снова наступило время специализации — в виде чипа для матричных вычислений, такого как Google TPU. Это специализированный процессор, разработанный Google для ускорения операций, связанных с машинным обучением, в частности для работы с глубокими нейронными сетями.

- Подобная история произошла и с графическим «железом» в домашних компьютерах: от специализированных чипов для 2D-графики в старых компьютерах Atari 8-бит и Amiga к программному управлению видеобуфером в PC-совместимых машинах.

- Далее: от специализированных 3D-ускорителей к графическим процессорам для вычислений общего назначения (GPGPU).

- В GPGPU тоже наметилась специализация в виде RT-ускорителей трассировки лучей и тензорных ускорителей для задач машинного обучения.

- Схожий переход к специализации изначально «однородного» универсального решения заметен в области FPGA: помимо однородных ячеек программируемой логики, на FPGA-чипе стали появляться DSP-ячейки, блочная память и даже матрицы спецпроцессоров с архитектурой VLIW (AMD Versal).

В статье Макимото написал о грядущей стандартизации типов ускорителей и введении ячеек FPGA в состав системы на кристалле, а также об использовании универсального энергонезависимого типа памяти, заменяющего на кристалле прочие типы памяти. Такие решения пока недоступны, и складывается ощущение, что выполнение закона волны Макимото замедляется сегодня примерно в той же степени, что и закон Мура.

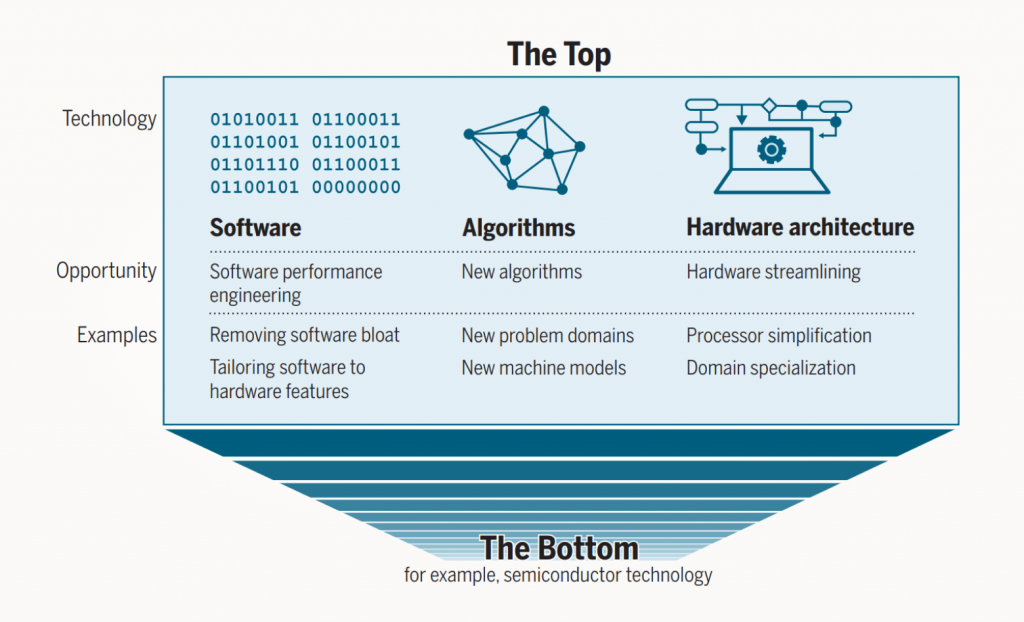

«There's plenty of room at the Top: What will drive computer performance after Moore’s law?», Charles E. Leiserson et al

Вообразим себе альтернативную реальность, где закон Деннарда все еще продолжает действовать, а выполнение закона Мура не замедлилось. Это мир, где всем вполне достаточно одноядерного процессора Pentium, теперь уже с частотой в сотни ГГц. Это мир, где новые оптимизации кода и новые аппаратные архитектуры не имеют особого значения, ведь достаточно просто дождаться перехода на следующий техпроцесс с автоматическим улучшением характеристик процессора общего назначения. К счастью или несчастью, но наша реальность не позволяет расслабиться.

Закон Деннарда перестал действовать еще в 2005 году и с тех пор тактовую частоту безнаказанно для энергетического бюджета микросхемы повышать уже невозможно. Решение с многоядерными универсальными процессорами тоже себя исчерпало. «Темный кремний» побуждает обращаться к специализации.

В статье приведен пример оптимизации кода для перемножения матриц в качестве иллюстрации того, что разница между реализациями на разных языках программирования невелика по сравнению с вариантом, где широко используются особенности аппаратной архитектуры, на которой выполняется код.

В этой связи мне вспомнился еще более яркий пример, описанный в твите Джо Армстронга, создателя языка Erlang:

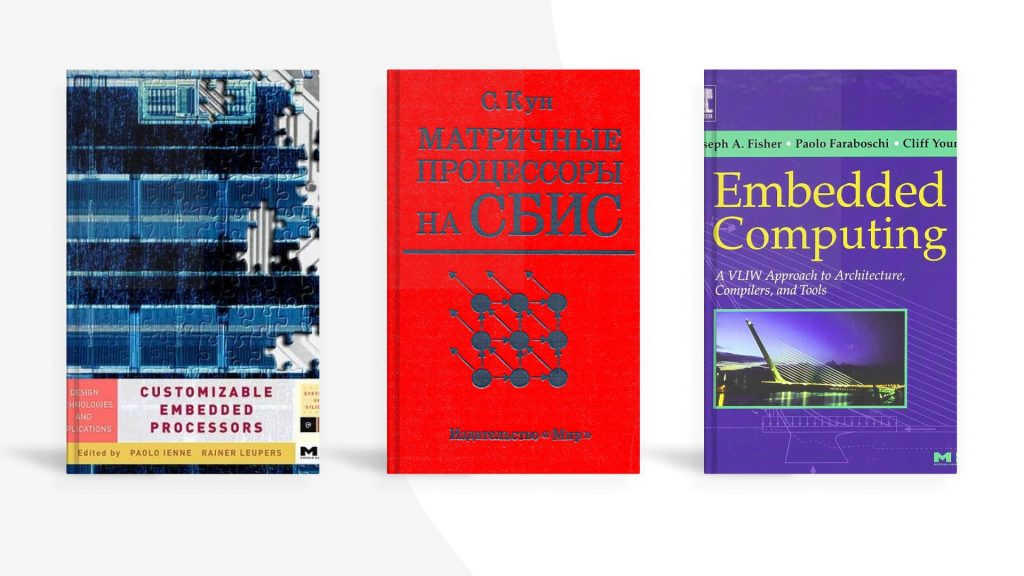

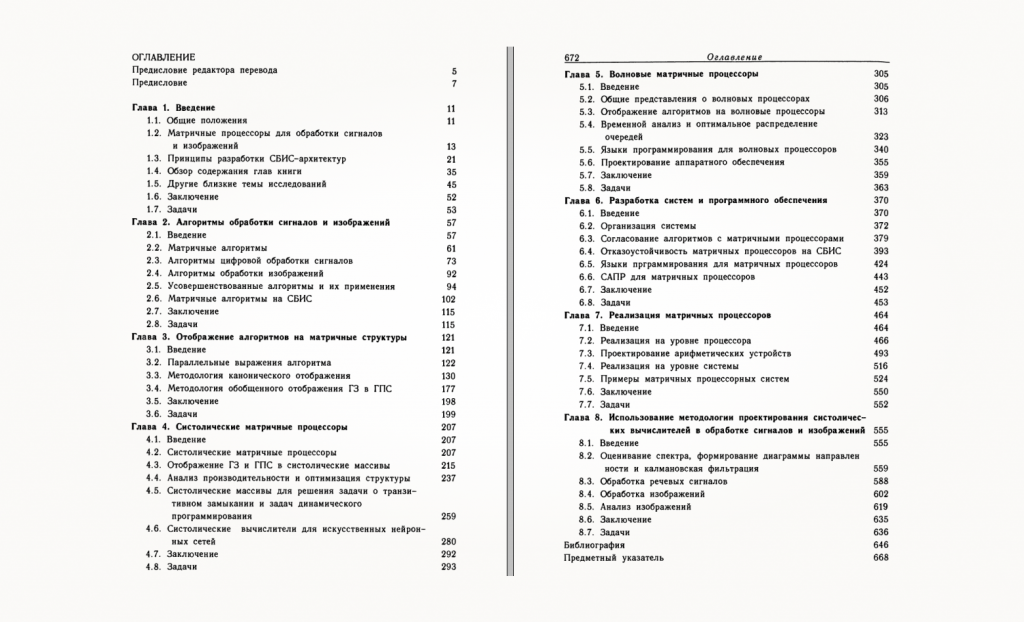

«Матричные процессоры на СБИС», Сунь Кун

Эта книга — подтверждение известной фразы о том, что новое — хорошо забытое старое.

Автор книги Сунь Кун — изобретатель систолического массива, одного из вариантов матричного процессора. В систолическом массиве вычисления и обмены данными между ПЭ происходят по синхронной схеме. Современный пример такого массива — блок перемножения матриц в Google TPU. Крупноблочные реконфигурируемые матрицы (CGRA), набирающие сегодня популярность в области спецвычислений, — это тоже пример систолического массива, в котором ПЭ содержат программируемое арифметико-логическое устройство.

Еще одним интересным вариантом архитектуры матричного процессора является волновой процессор, которому в книге посвящена отдельная глава. Такой процессор представляет собой матрицу асинхронно работающих программируемых ПЭ, управляемых потоком данных. Современные реализации волновых процессоров содержат специализированные RISC- или VLIW-ядра в качестве ПЭ.

В целом, эта книга — фундаментальный труд, где рассматриваются вопросы проектирования матричных процессоров, способы компиляции кода для них, а также применение рассматриваемых архитектур в задачах из области цифровой обработки сигналов.

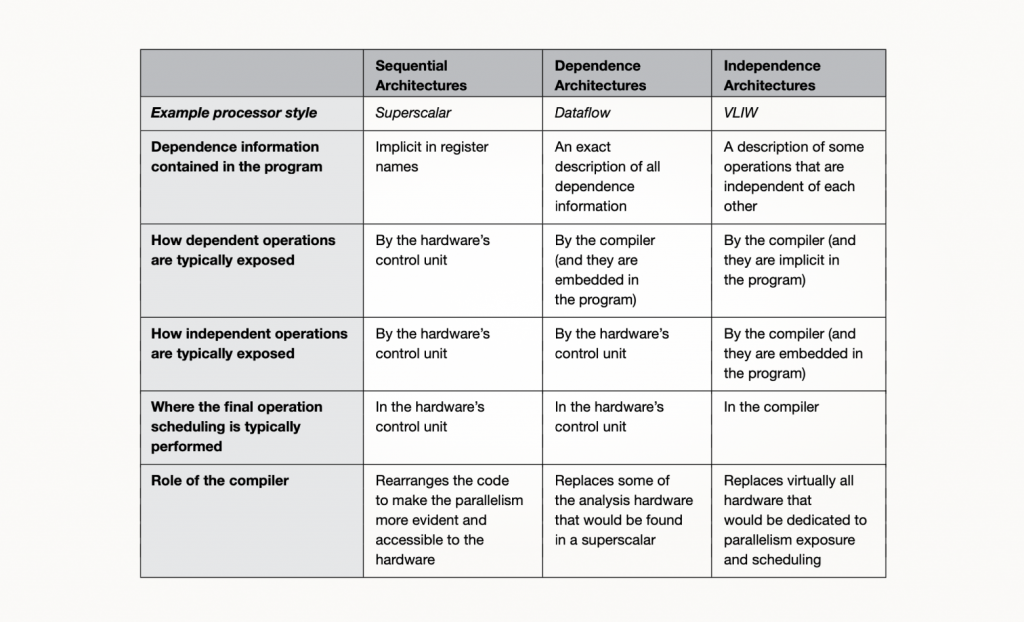

«Embedded Computing: A VLIW Approach to Architecture, Compilers and Tools», Joseph A. Fisher et al

В 2005 году появился еще один фундаментальный труд — от Джозефа Фишера, автора архитектуры VLIW. Объективности ради стоит упомянуть, что VLIW-процессоры были известны и до появления первой работы Фишера, о чем я писал в заметке. Основная идея архитектуры VLIW емко выражается названием одной из ранних статей Фишера — «Parallel Processing: A Smart Compiler and a Dumb Machine».

Проектированию VLIW-архитектуры с учетом ее специализации в книге отведено не так много места. Ключевые параметры специализации для VLIW — это количество параллельно работающих функциональных узлов и поддерживаемые ими операции. Конкретные значения этих параметров могут быть получены путем анализа программных реализаций алгоритмов, на выполнение которых ориентирован проектируемый спецпроцессор.

Важнейшее условие успешного применения VLIW — наличие компилятора, генерирующего качественный параллельный код. В этом смысле автор книги представляет собой образец современного проектировщика спецпроцессоров, поскольку он должен быть в некоторой степени «компиляторщиком». В тексте достаточно много места уделено вопросам компиляции, в частности методам планирования команд.

Сегодня VLIW-спецпроцессоры широко применяются в качестве ускорителей для задач машинного обучения. Самый, пожалуй, яркий пример — Google TPU, скалярный блок которого имеет архитектуру VLIW.

«Customizable Embedded Processors: Design Technologies and Applications», Paolo Ienne, Rainer Leupers

Конфигурируемые процессорные архитектуры, которым отведена часть текста, сегодня используются достаточно широко. Среди них Cadence Tensilica Xtensa, Synopsis ARC Cores и, конечно, конструкторы спецпроцессоров на базе RISC-V.

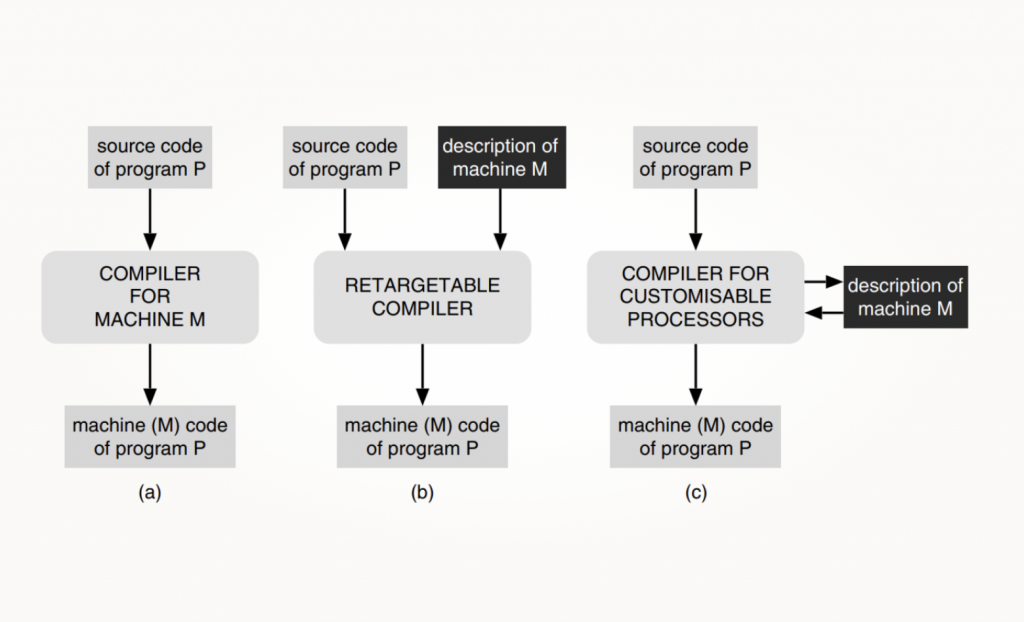

Иное дело — языки описания архитектуры (ADL). Описываемые в книге перенацеливаемые компиляторы и генераторы спецпроцессоров на базе ADL в основном существуют лишь в академических источниках. Единственное, но впечатляющее исключение — ASIP Designer от компании Synopsys. Это генератор спецпроцессоров (а также инструментальных средств: компиляторов, симуляторов

В нескольких главах рассматриваются подходы к проектированию спецпроцессоров, полноценная реализация которых все еще является делом будущего. Речь об автоматическом синтезе специализированных расширений команд на основе анализа программного кода, а также о слиянии трактов данных для синтеза реконфигурируемых ускорителей.